# RK3168 Technical Reference Manual

Revision2.1 Dec. 2013

### **Revision History**

| Date       | Revision | Description                                  |

|------------|----------|----------------------------------------------|

| 2012-07-19 | 1.0      | Initial Release                              |

| 2012-09-08 | 2.0      | Update GRF, CRU and PMU section              |

| 2013-12-14 | 2.1      | Update io list,Power supply sequence for USB |

|            |          |                                              |

### **Table of Content**

| Table of Content                                                  |          |

|-------------------------------------------------------------------|----------|

| Figure Index                                                      |          |

| Table Index                                                       |          |

| Acronym Descriptions                                              |          |

| Chapter 1 Introduction                                            |          |

| 1.1 Features                                                      | 23       |

| 1.1.1 MicroProcessor                                              | 23       |

| 1.1.2 Memory Organization                                         | 24       |

| 1.1.3 Internal Memory                                             |          |

| 1.1.4 External Memory or Storage device                           |          |

| 1.1.5 System Component                                            |          |

| 1.1.6 Video CODEC                                                 | 28       |

| 1.1.7 JPEG CODEC                                                  |          |

| 1.1.8 Image Enhancement                                           | 29       |

| 1.1.9 Graphics Engine                                             | 30       |

| 1.1.10 Video IN/OUT                                               | 32<br>22 |

| 1.1.12 Connectivity                                               |          |

| 1.1.13 Others                                                     |          |

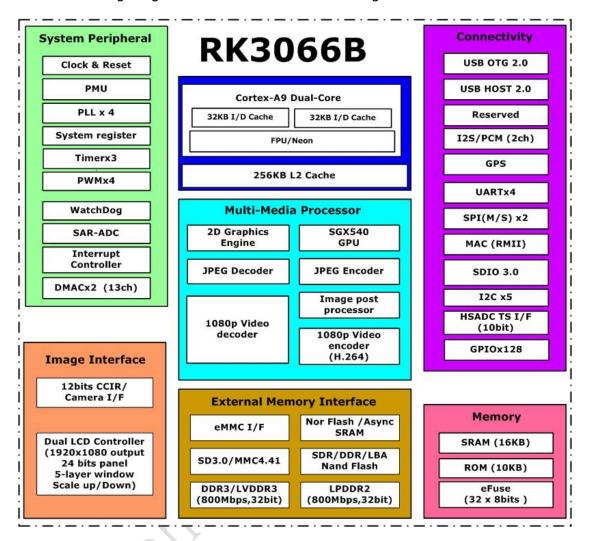

| 1.2 Block Diagram                                                 | 35       |

| 1.2 block blagfail                                                | 30       |

| 1.2 Block Diagram  1.3 Pin Description                            | 36       |

| 1.3.1 RK3168 power/ground IO descriptions                         | 36       |

| 1.3.2 RK3168 function IO descriptions                             | 39       |

| 1.3.3 IO pin name descriptions                                    |          |

| 1.3.4 RK3168 IO Type                                              | 53       |

| 1.4 Package information                                           | 53       |

| 1.4.1 Dimension                                                   | 52       |

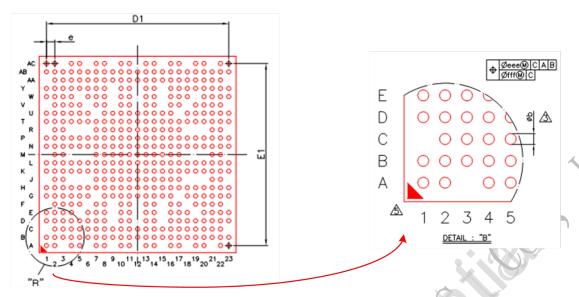

| 1.4.2 Ball Map                                                    |          |

| 1.4.3 Ball Pin Number Order                                       |          |

| 1.5 Electrical Specification                                      |          |

|                                                                   |          |

| 1.5.1 Absolute Maximum Ratings                                    | 64       |

| 1.5.2 Recommended Operating Conditions                            |          |

| 1.5.3 DC Characteristics                                          |          |

| 1.5.4 Recommended Operating Frequency                             |          |

| 1.5.5 Electrical Characteristics for General IO                   |          |

| 1.5.7 Electrical Characteristics for PLL                          |          |

| 1.5.8 Electrical Characteristics for USB OTG/Host2.0 Interface    |          |

| 1.5.9 Electrical Characteristics for DDR IO                       |          |

| 1.5.10 Electrical Characteristics for eFuse                       |          |

| 1.6 Hardware Guideline                                            |          |

|                                                                   |          |

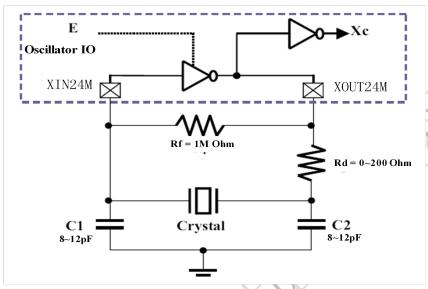

| 1.6.1 Reference design for RK3168 oscillator PCB connection       |          |

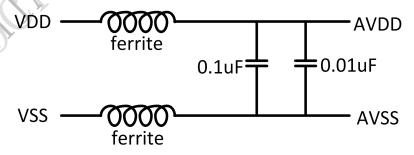

| 1.6.2 Reference design for PLL PCB connection                     |          |

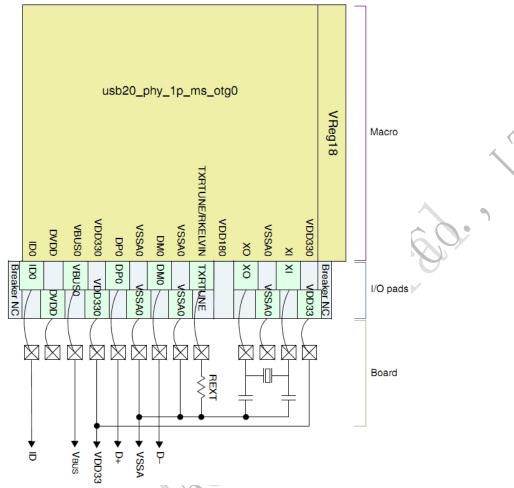

| 1.6.3 Reference design for USB OTG/Host2.0 connection             |          |

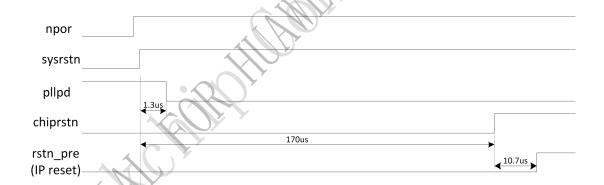

| 1.6.4 RK3168 Power up/down sequence requirement                   |          |

| 1.6.5 RK3168 Power on reset descriptionsChapter 2 System Overview |          |

| CHAPTER 7 2 2421 CART ALEM                                        | / /      |

| 2.1 Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 2.2 System Boot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                        |

| 2.3 System Interrupt connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                        |

| 2.4 System DMA hardware request connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81                        |

| Chapter 3 CRU (Clock & Reset Unit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |

| Chapter 4 PMU (Power Management Unit)4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83                        |

| 4.1.1 Features Chapter 5 System Security 5.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                        |

| Chapter 6 System Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84                        |

| 6.1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84<br>85                  |

| 6.3 Function description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85                        |

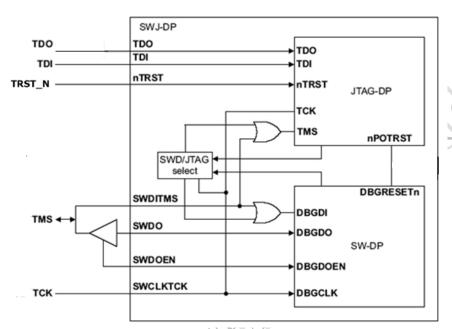

| 6.3.1 DAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86<br>86<br>86            |

| 6.4.1 DAP APB-AP register summary 6.4.2 DAP APB-AP Detailed Register Description 6.4.3 DAP AHB-AP register summary 6.4.4 DAP AHB-AP Detailed Register Description 6.4.5 DAP-ROM register summary 6.4.6 DAP-ROM Detailed Register Description 6.4.7 PTM register summary 6.4.8 PTM Detailed Register Description 6.4.9 Funnel register summary 6.4.10 Funnel register details 6.4.11 CTI register details 6.4.12 CTI register summary 6.4.13 TPIU register summary 6.4.14 TPIU detailed register description 6.5 Interface description | 8790939596106112113120121 |

| 6.5.1 DAP SWJ-DP interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 128<br>130                |

| 7.2 Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 130                       |

| 7.3 Register description                                                               | 131                             |

|----------------------------------------------------------------------------------------|---------------------------------|

| 7.3.1 System Registe                                                                   | 134<br>229                      |

| 8.2 Block Diagram                                                                      | 230                             |

| 8.3 Function description                                                               | 230                             |

| 8.4 Register description                                                               | 230                             |

| 8.4.1 Registers Summary<br>8.4.2 Detail Registers Description<br>8.5 Application Notes | 234                             |

| 8.5.1 Address filtering                                                                |                                 |

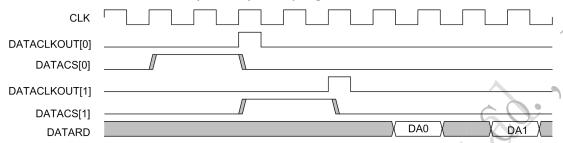

| 10.2 Block Diagram                                                                     | 270                             |

| 10.3 Function Description                                                              | 271                             |

| 10.3.1 Introduction                                                                    | 272                             |

| 10.4.1 Register summary                                                                | 275                             |

| 10.6 Interface Description                                                             | 288                             |

| 10.7 Application Notes                                                                 | 289                             |

| 10.7.1 Using the APB slave interfaces                                                  | 289<br>293<br>294<br>295<br>296 |

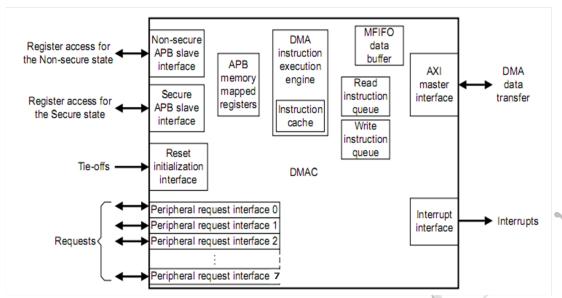

| Chapter 11 DMAC1(DMA Controller)                                                       | 297                             |

| 11.1 Overview                                                                          | 297                             |

| 11.2 Block Diagram                                                                     | 297                             |

| 11.3 Function Description                                                              | 298                             |

| 11.4 Register Description                                                              | 298                             |

|    |       | 11.4.1 Register summary11.4.2 Detail Register Description                                         |            |

|----|-------|---------------------------------------------------------------------------------------------------|------------|

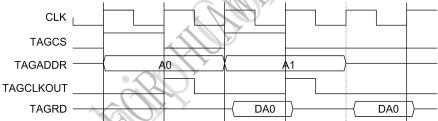

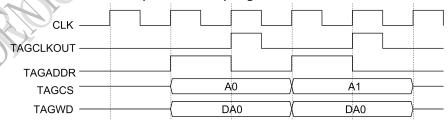

|    | 11.5  | Timing Diagram                                                                                    | 314        |

|    | 11.6  | Interface Description                                                                             | 314        |

|    | 11.7  | Application Notes                                                                                 | 315        |

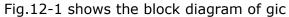

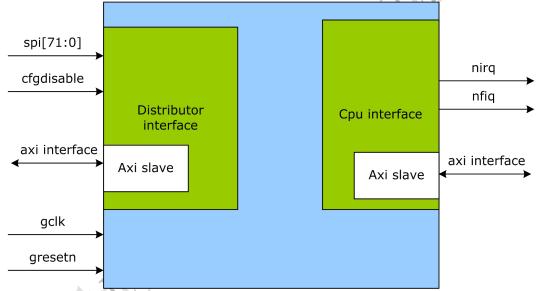

| Cł | napte | r 12 GIC(General Interrupt Controller)                                                            | 316        |

|    | 12.1  | Overview                                                                                          | 316        |

|    | 12.2  | Block Diagram                                                                                     | 316        |

|    | 12.3  | Function Description                                                                              | 316        |

|    |       | 12.3.1 The Distributor                                                                            | 317        |

|    |       | 12.3.2 CPU interface                                                                              | 318<br>318 |

|    | 12.4  | Register Description                                                                              |            |

|    |       | 12.4.1 GIC Distributor interface register summary                                                 | 320        |

|    |       | 12.4.2 GIC Distributor interface detail register description                                      | .320       |

|    |       | 12.4.3 GIC CPU interface register summary                                                         |            |

|    |       | 12.4.4 GIC CPU interface detail register description                                              |            |

|    | 12.5  | Interface Description                                                                             | 329        |

|    | 12.6  | Application Notes                                                                                 | 329        |

|    |       | 12.6.1 General handling of interrupts                                                             |            |

|    |       | 12.6.2 Interrupt prioritization                                                                   |            |

|    |       | 12.6.3 The effect of the Security Extensions on interrupt handling.                               |            |

| CŁ | anto  | 12.6.4 The effect of Security Extensions on interrupt priorityr 13 DMC (Dynamic Memory Interface) |            |

|    | •     | Overview                                                                                          |            |

|    |       | A 4                                                                                               |            |

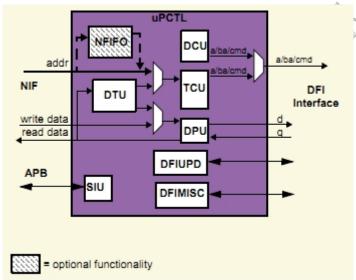

|    | 13.2  | Block Diagram                                                                                     | 335        |

|    | 13.3  | Function description                                                                              | 336        |

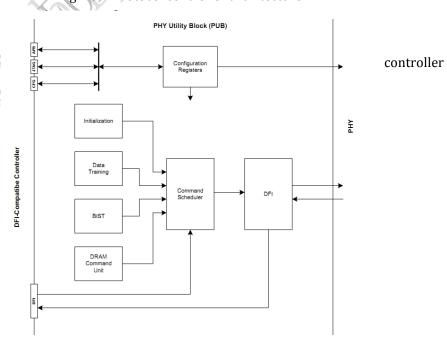

|    | 13.4  | DDR PHY                                                                                           | 337        |

|    |       | 13.4.1 DDR PHY Overview                                                                           | 337        |

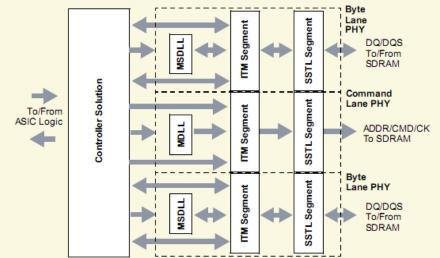

|    |       | 13.4.2 Lane-Based Architecture                                                                    |            |

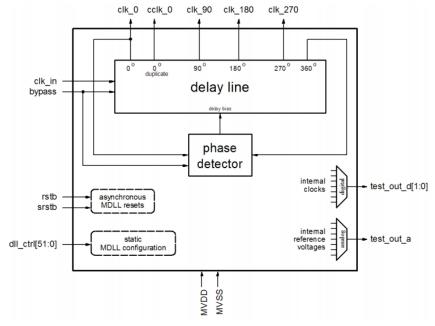

|    |       | 13.4.3 Master DLL(MDLL)                                                                           |            |

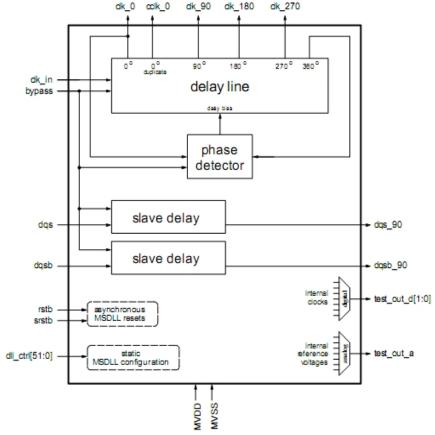

|    |       | 13.4.4 Master-Slave DLL(MSDLL)                                                                    |            |

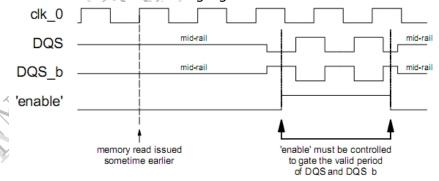

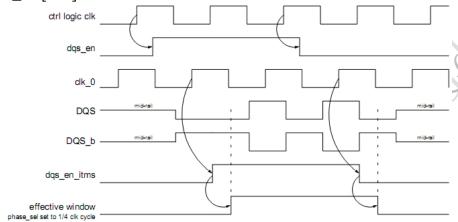

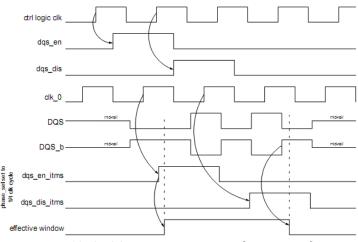

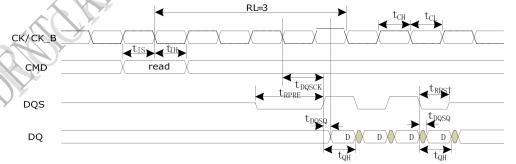

|    |       | 13.4.5 DQS Gating                                                                                 |            |

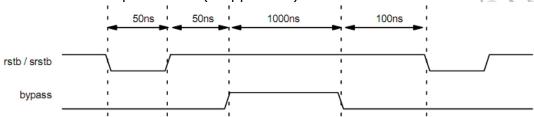

|    | 12 E  | 13.4.6 Dynamic Strobe Drift Detection                                                             |            |

|    | 13.5  |                                                                                                   |            |

|    |       | 13.5.1 Registers Summary                                                                          |            |

|    | 12 6  | 13.5.2 Detail Registers Description                                                               |            |

|    | 13.0  | Timing Diagram                                                                                    |            |

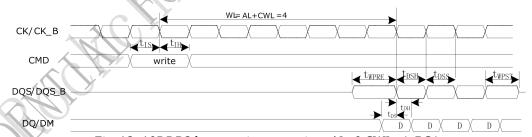

|    |       | 13.6.1 DDR3 Read/Write Access Timing                                                              |            |

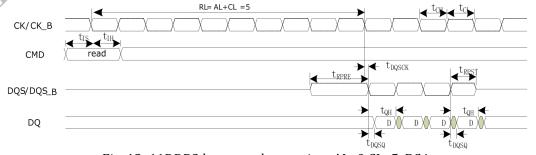

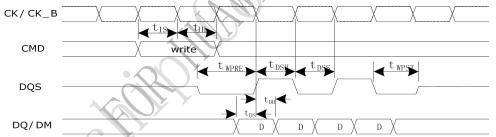

|    | 10 -  | 13.6.2 LPDDR2 Read/Write Access Timing                                                            |            |

|    | 13/   | Interface description                                                                             | 557        |

| 13.8 Application Notes                   | 558 |

|------------------------------------------|-----|

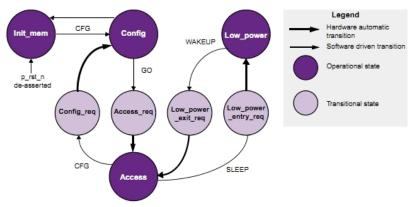

| 13.8.1 State transition of PCTL          |     |

| 13.8.3 MDLL and MSDLL Reset Requirements |     |

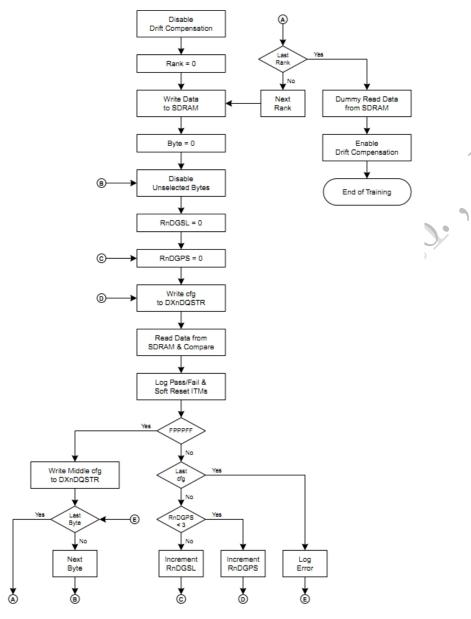

| 13.8.4 Data Training                     |     |

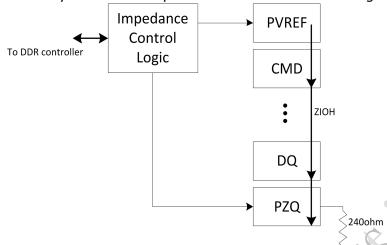

| 13.8.5 Impedance Calibration             |     |

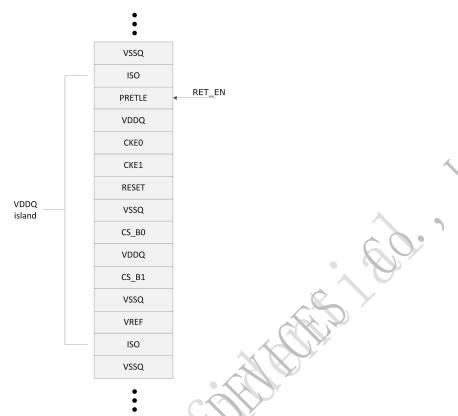

| 13.8.6 Retention Functional              |     |

| 13.8.7 Low Power Operation               |     |

| 13.8.8 PHY Power Down                    |     |

| 13.8.9 Dynamic ODT for I/Os              |     |

| Chapter 14 SMC(Static Memory Controller) |     |

| 14.1 Overview                            |     |

|                                          |     |

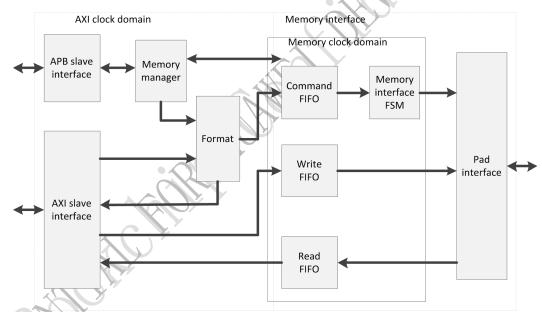

| 14.2 Block Diagram                       |     |

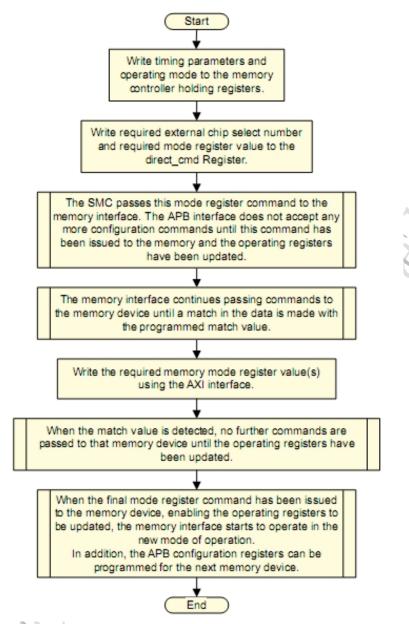

| 14.3 Function Description                | 575 |

| 14.3.1 APB slave interface               | 575 |

| 14.3.2 Format                            | 576 |

| 14.3.3 Memory manager                    | 577 |

| 14.3.4 Memory interface                  |     |

| 14.3.5 Pad interface                     |     |

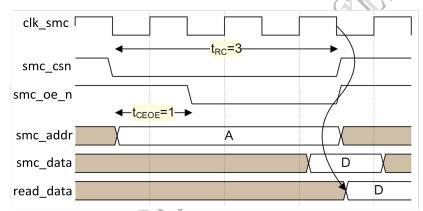

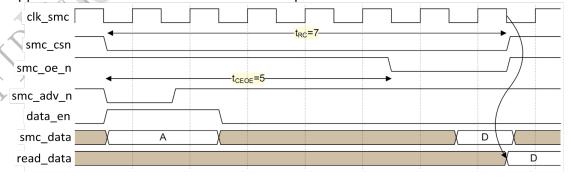

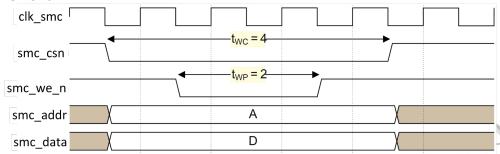

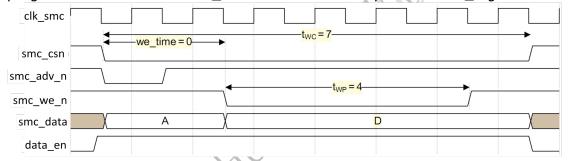

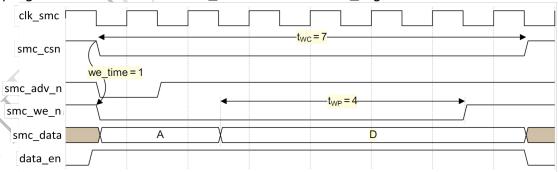

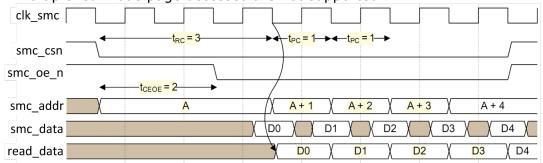

| 14.3.6 SRAM interface timing diagrams    | 579 |

| 14.4 Register Description                | 581 |

| 14.4.1 Registers Summary                 |     |

| 14.4.2 Detail Register Description       |     |

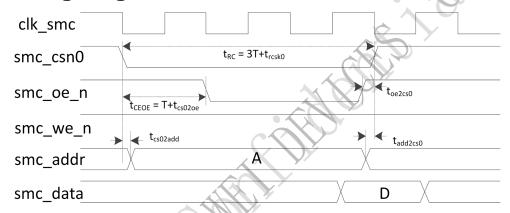

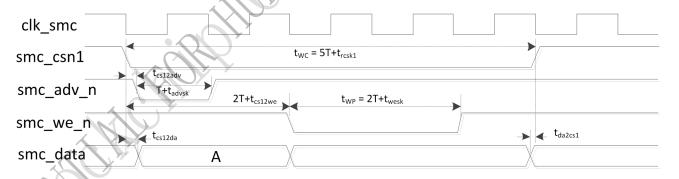

| 14.5 Timing Diagram                      |     |

| 14.6 Interface Description               | 592 |

| 14.7 Application Notes                   | 593 |

| 14.7.1 multiplexed address/data mode     | 593 |

| Chapter 15 NandC(Nand Flash Controller)  |     |

| 15.1 Overview                            |     |

| 15.1.1 Features                          | 594 |

| Chapter 16 eMMC Interface                |     |

| 16.1 Overview                            |     |

| Chapter 17 SD/MMC Card Host Controller   | 596 |

| 17.1 Overview                            |     |

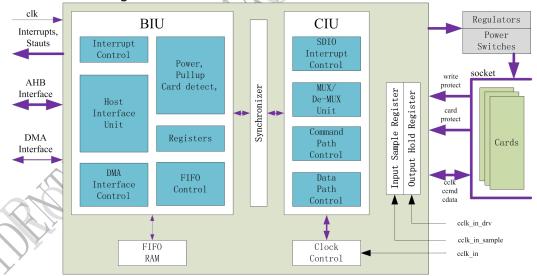

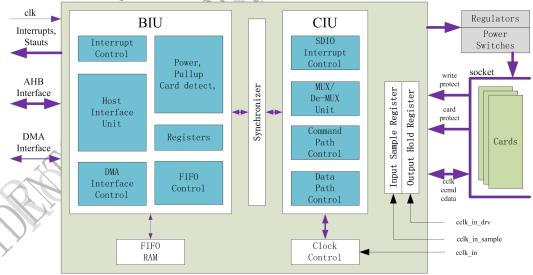

| 17.2 Block Diagram                       | 596 |

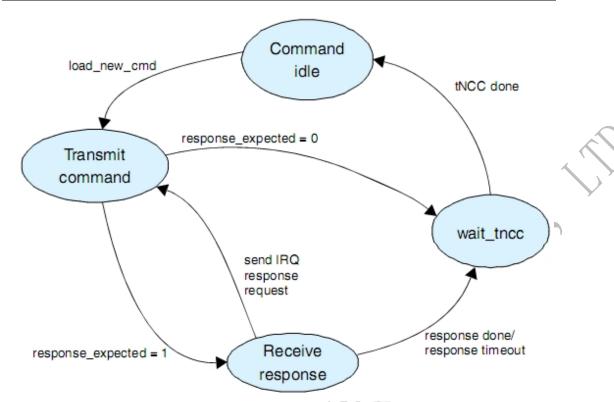

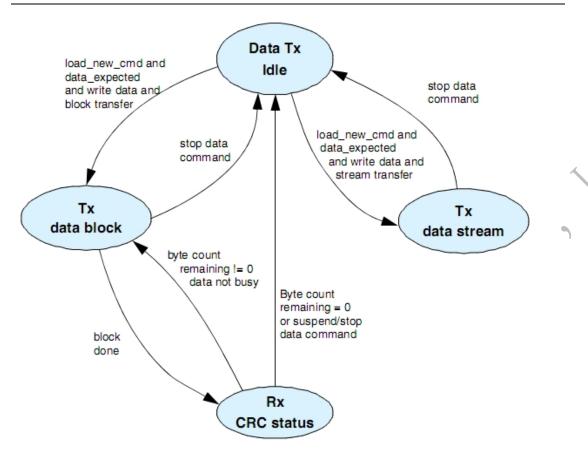

| 17.3 Function description                | 597 |

| 17.3.1 Bus Interface Unit                |     |

| 17.3.2 Card Interface Unit               |     |

|                                          |     |

| 17.4 Register description                |     |

| 17.4.1 Register Summary                  |     |

| 17.4.2 Detail Register Description       | 614 |

| 17.5 Timing Diagram                      | 636 |

| 17.6 Interface description                                                                          | 636        |

|-----------------------------------------------------------------------------------------------------|------------|

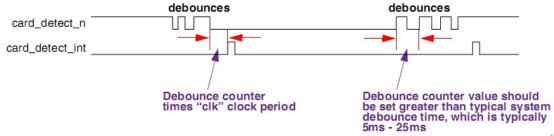

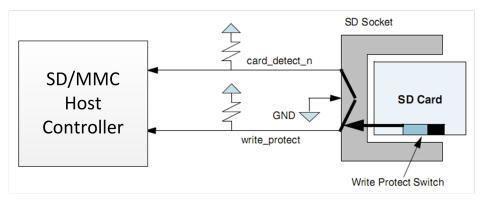

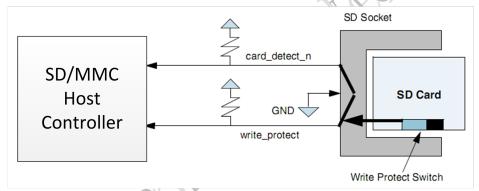

| 17.6.1 Card-Detect and Write-Protect Mechanism                                                      | 637        |

| 17.7 Application Notes                                                                              | 638        |

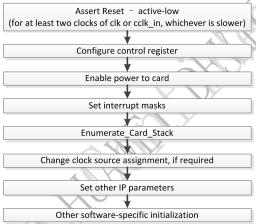

| 17.7.1 Software/Hardware Restriction17.7.2 Programming Sequence                                     | 640        |

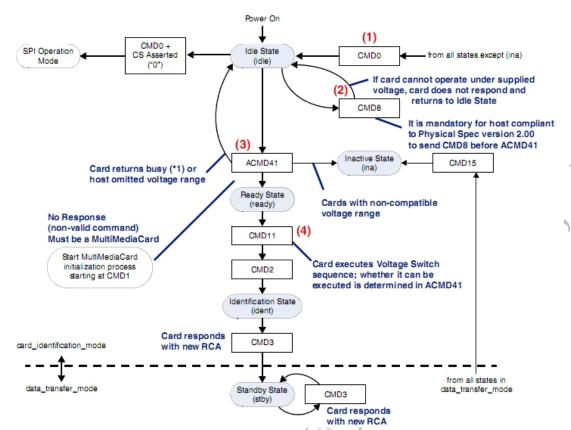

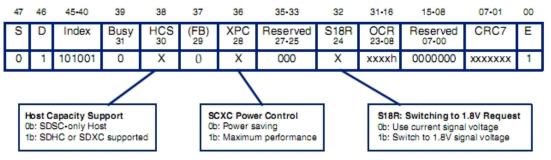

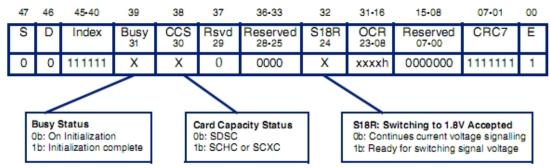

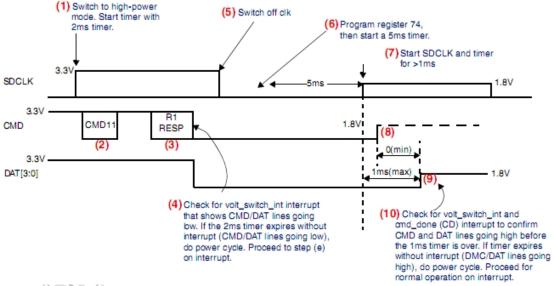

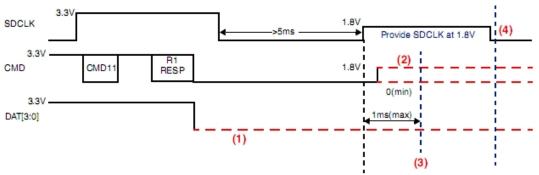

| 17.7.3 Programming SD/MMC Controller for Boot Operation 17.7.4 Voltage Switching and DDR Operations | 659        |

| 17.7.5 H/W Reset Operation                                                                          | 665        |

| 18.1.1 Features supported                                                                           |            |

| 18.1.2 Features not supported                                                                       | 665        |

|                                                                                                     |            |

| 18.3 Function Description                                                                           |            |

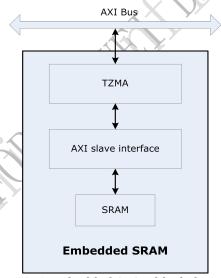

| 18.3.1 TZMA                                                                                         | 665        |

| 18.3.2 AXI slave interface18.3.3 Embedded SRAM access path                                          | 665<br>665 |

| Chapter 19 GPU (Graphics Process Unit)                                                              |            |

| 19.1 Overview                                                                                       | 666        |

| 19.1.1 GPU Architecture - Key Features                                                              |            |

| 19.1.2 2D Features19.1.3 3D Features                                                                |            |

| Chapter 20 VCODEC (Video encoder and decoder Unit)                                                  |            |

| 20.1 Overview                                                                                       |            |

| Chapter 21 IPP (Image Post Processor)                                                               | 669        |

| 21.1 Overview                                                                                       |            |

| 21.1.1 Features                                                                                     | 669        |

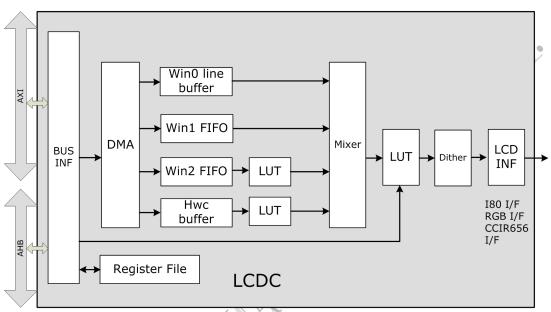

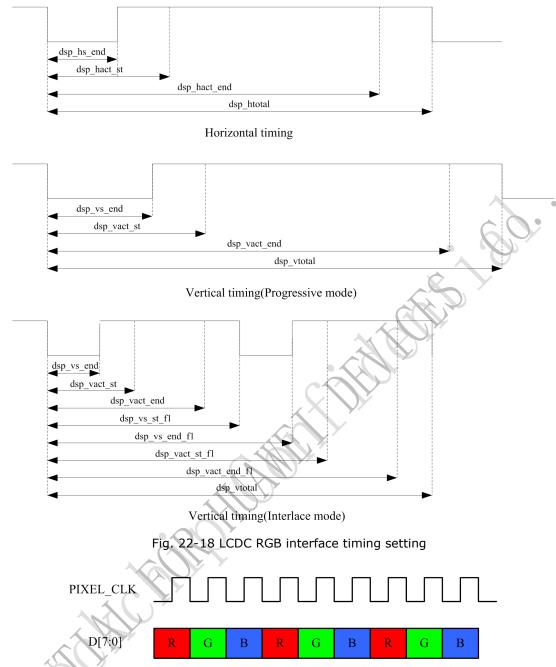

| Chapter 22 LCDC                                                                                     | 670        |

| 22.1 Overview                                                                                       | 670        |

| 22.1.1 Features                                                                                     | 670        |

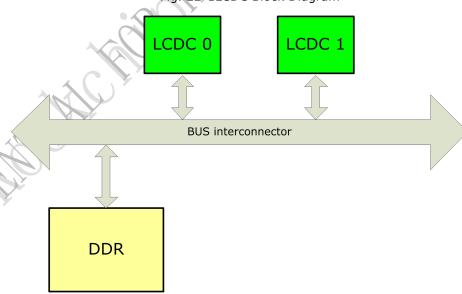

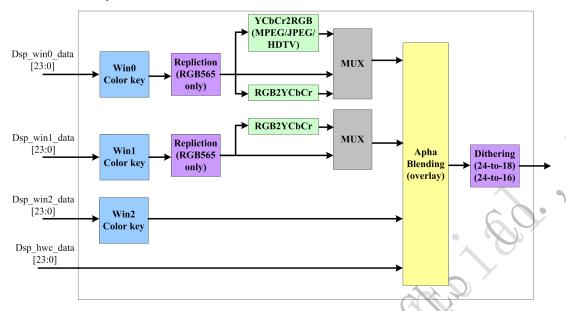

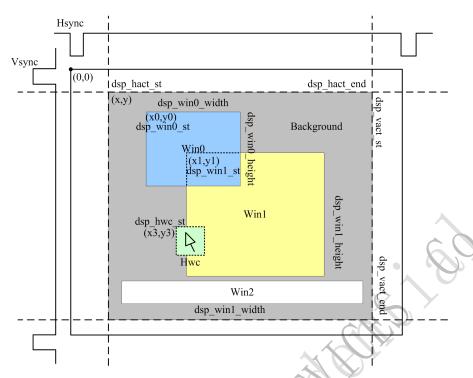

| 22.2 Block Diagram                                                                                  | 671        |

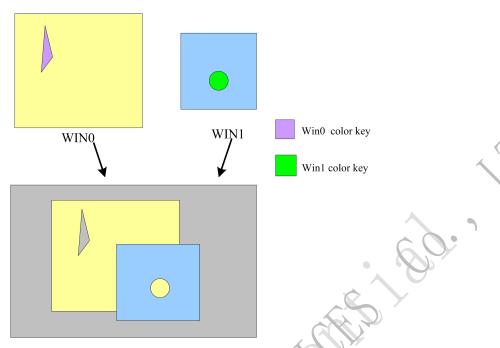

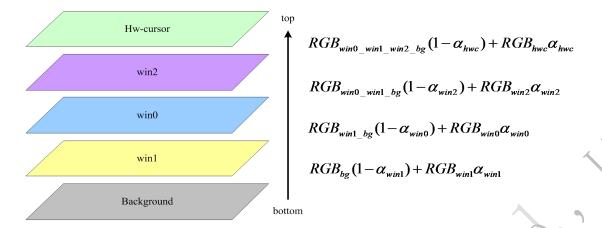

| 22.3 Function Description                                                                           | 672        |

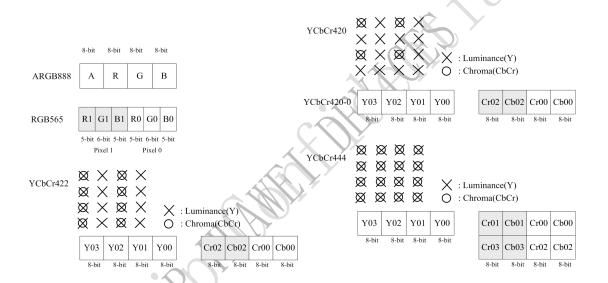

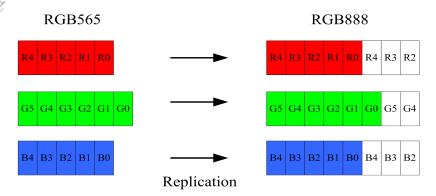

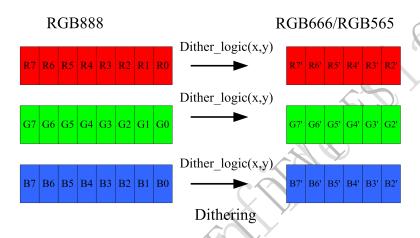

| 22.3.1 Data Format                                                                                  | 672        |

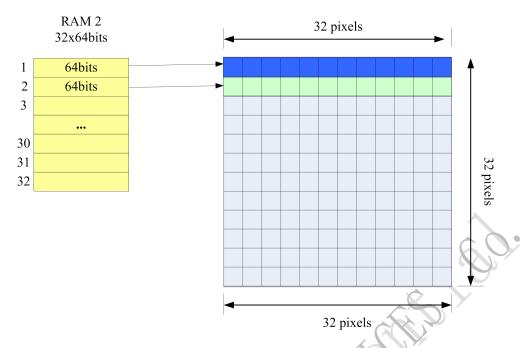

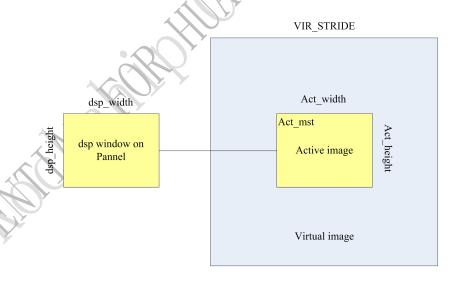

| 22.3.2 Virtual display                                                                              |            |

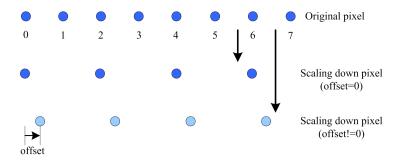

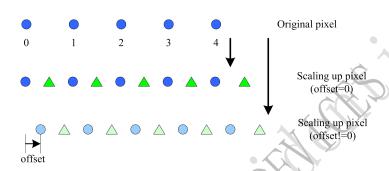

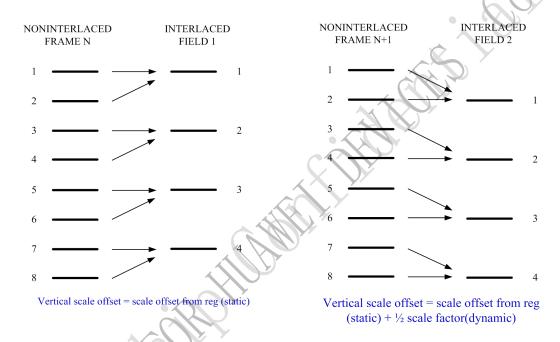

| 22.3.3 Scaling                                                                                      |            |

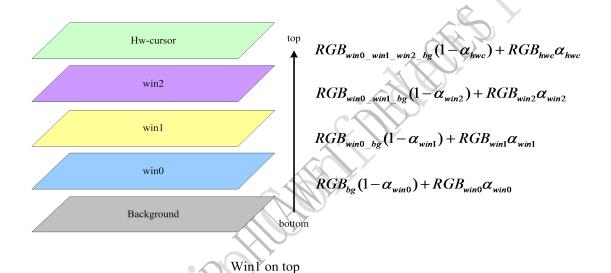

| 22.3.4 Overlay22.4 Register Description                                                             |            |

| ·                                                                                                   |            |

| 22.4.1 Register Summary22.4.2 Detail Register Description                                           |            |

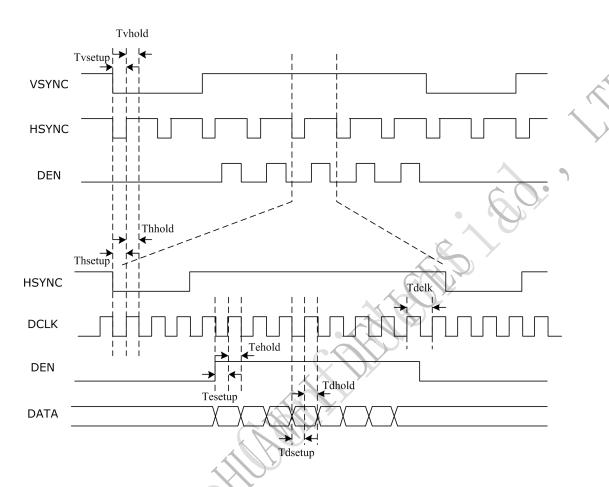

| 22.5 Timing Diagram                                                                                 |            |

|                                                                                                     |            |

| 22.6 Interface Description                                                                          | 099        |

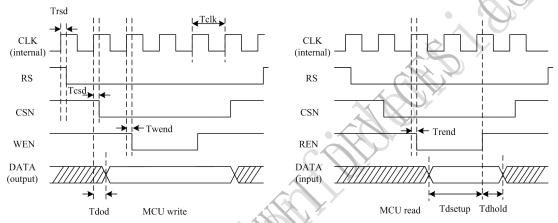

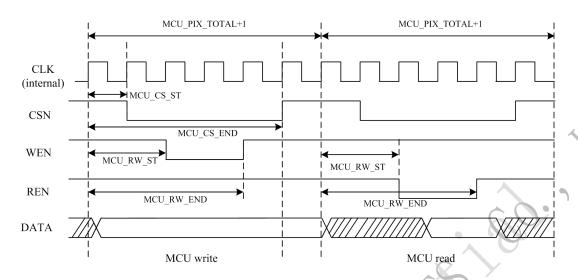

| 22.6.1 LCDC0 IOs22.6.2 LCDC1 IOs22.6.3 Pin Definition22.6.4 RGB Interface | 699<br>699 |

|---------------------------------------------------------------------------|------------|

| 22.6.5 MCU Interface (i80)                                                |            |

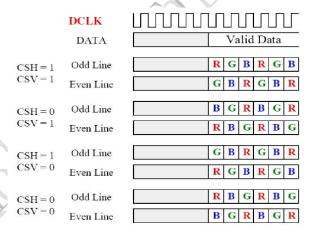

| 22.6.6 RGB Delta InterfaceChapter 23 RGA                                  |            |

| 23.1 Overview                                                             |            |

| 23.1.1 Features                                                           |            |

| Chapter 24 Camera Interface                                               |            |

| 24.1 Overview                                                             |            |

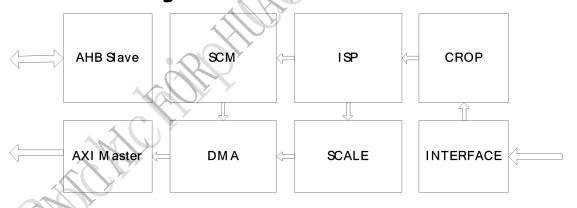

| 24.2 Block Diagram                                                        | 703        |

| 24.3 Function description                                                 | 704        |

| 24.4 Register description                                                 |            |

| 24.4.1 Register Summary                                                   | 707        |

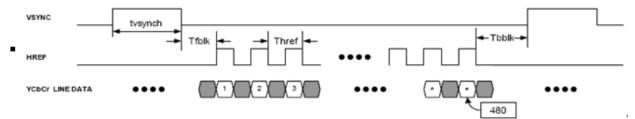

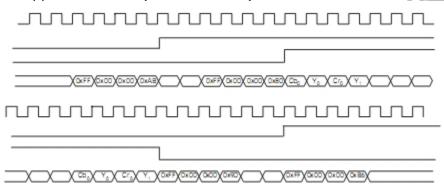

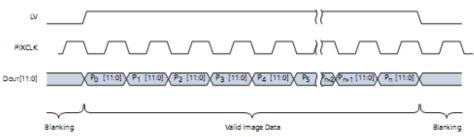

| 24.4.2 Detail Register Description24.5 Timing Diagram                     | 708        |

|                                                                           |            |

| 24.6 erface description                                                   | 720        |

| 24.7 Application Notes                                                    | 720        |

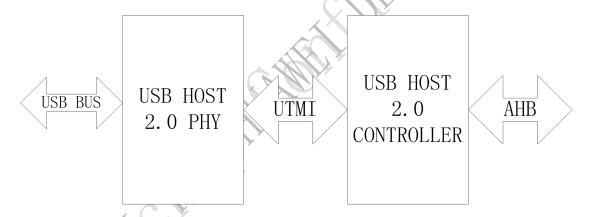

| Chapter 25 USB Host2.0                                                    | 722        |

| 25.1 Overview                                                             | 722        |

| 25.1.1 Features                                                           | 722        |

| 25.2 Block Diagram                                                        | 722        |

| 25.2.1 USB HOST 2.0 Controller Function                                   | 722        |

| 25.2.2 USB HOST 2.0 PHY Function                                          | 723        |

| 25.3 USB Host2.0 Controller                                               | 723        |

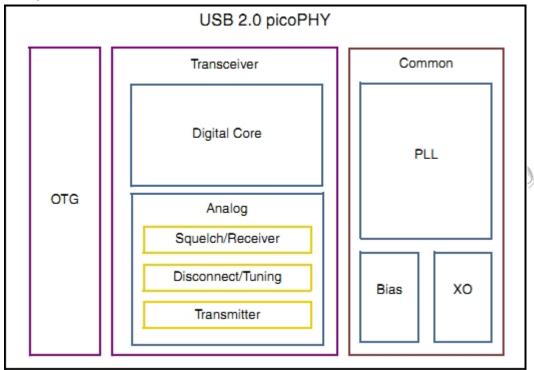

| 25.4 USB Host2.0 PHY                                                      | 724        |

| 25.4.1 Block Diagram                                                      | 725        |

| 25.5 Register description                                                 | 725        |

| 25.5.1 Registers Summary                                                  |            |

| 25.5.2 Registers Description                                              |            |

| 25.6 Interface description                                                |            |

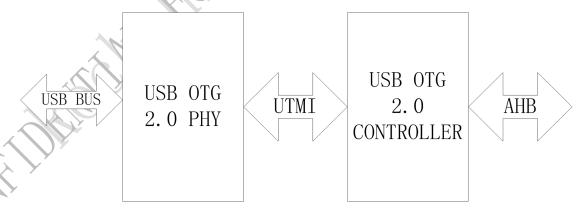

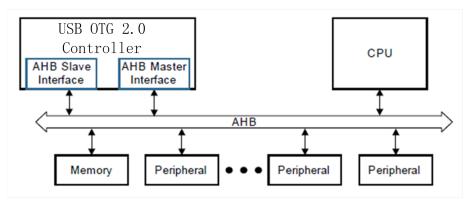

| Chapter 26 USB OTG2.0                                                     |            |

| 26.1 Overview                                                             | 731        |

| 26.1.1 Features                                                           | 731        |

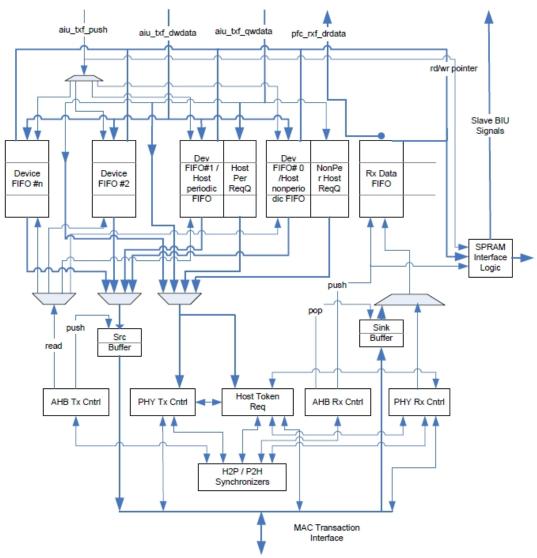

| 26.2 Block Diagram                                                        | 731        |

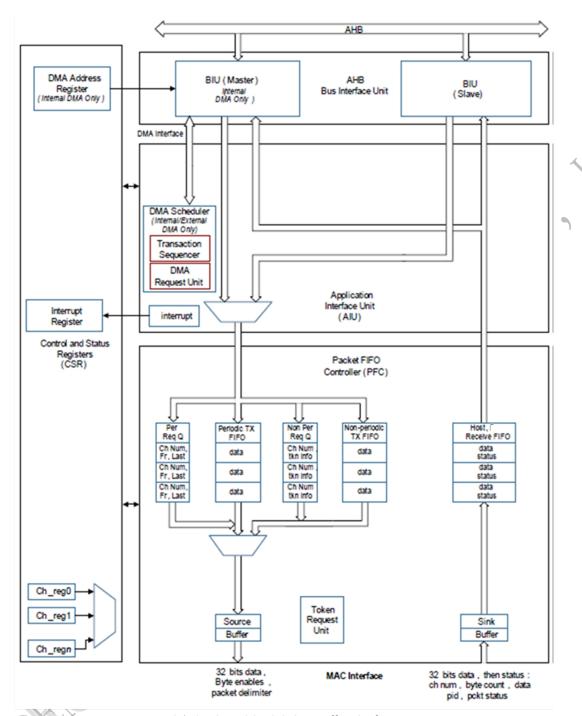

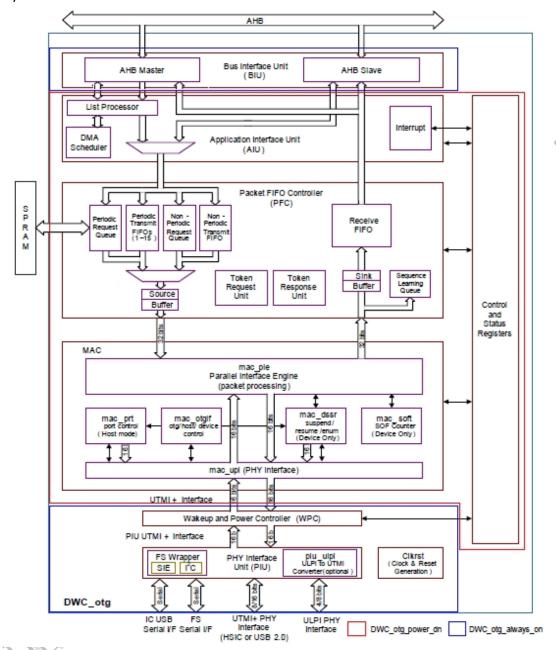

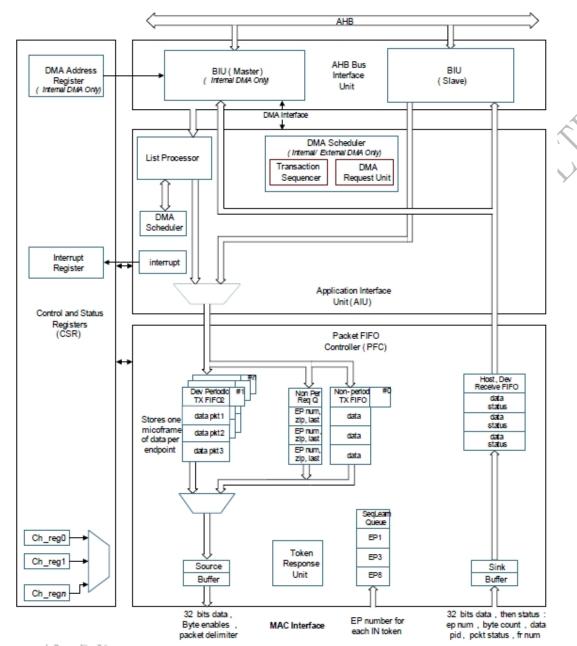

| 26.2.1 USB OTG 2.0 Controller Function                                    |            |

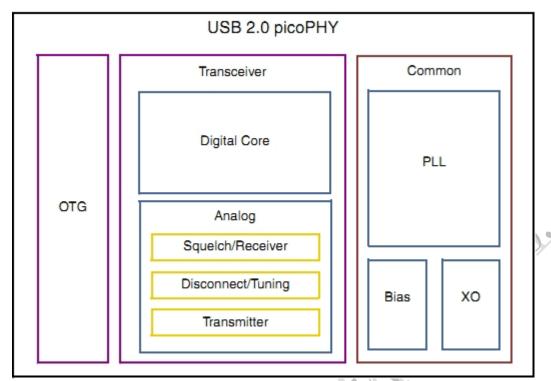

| 26.2.2 USB OTG 2.0 PHY Function                                           |            |

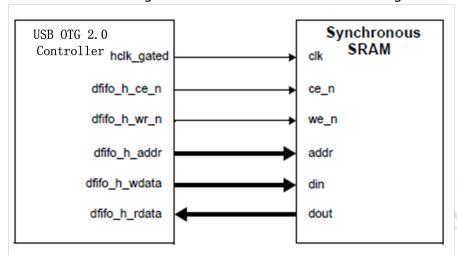

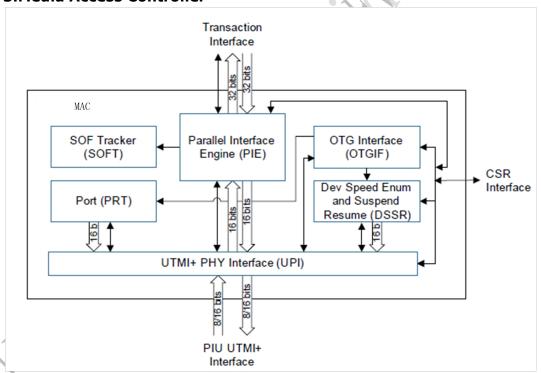

| 26.2.3 UTMI Interface26.3 USB OTG2.0 Controller                           |            |

|                                                                           |            |

| 26.3.1 Host Architercture                                                 | /34        |

| 26.3.2 Device Architercture                              |            |

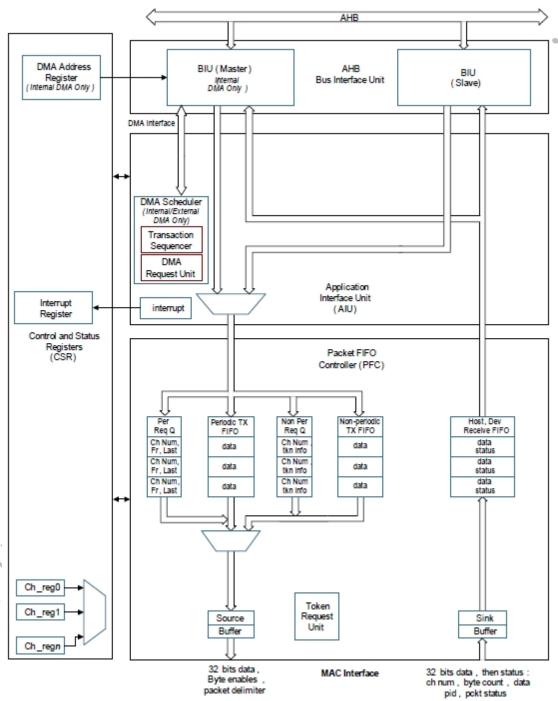

|----------------------------------------------------------|------------|

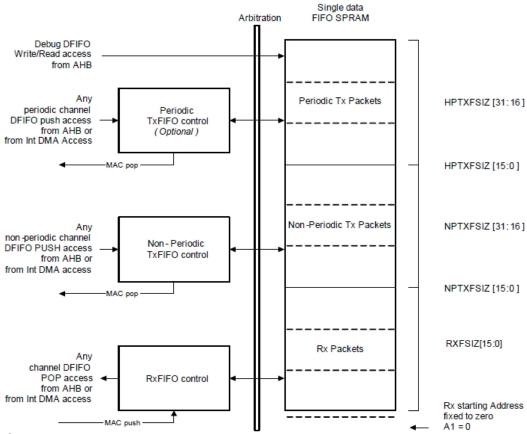

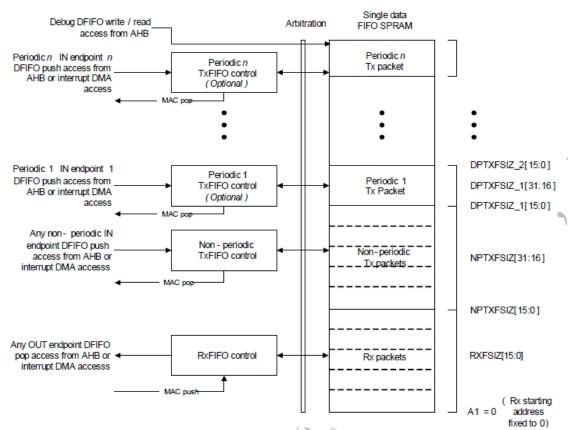

| 26.3.3 Internal DMA Mode26.3.4 FIFO Mapping              |            |

| 26.3.5 Sub-Module Architecture                           |            |

| 26.4 USB OTG2.0 PHY                                      |            |

| 26.4.1 Block Diagram                                     | 742        |

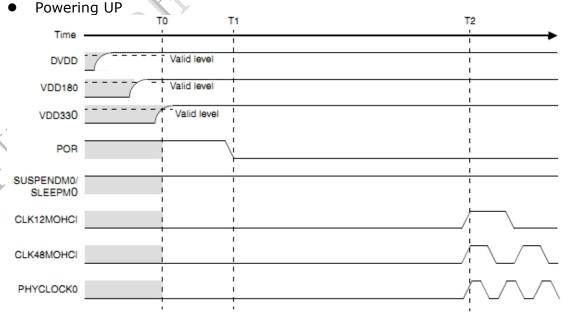

| 26.4.2 Powering Up and Powering Down                     |            |

| 26.4.3 Removing Power Supplies for Power Saving          |            |

| 26.5 Register description                                |            |

| 26.5.1 Register Summary                                  |            |

| 26.5.2 Detail Register Description                       |            |

| 26.6 Interface description                               |            |

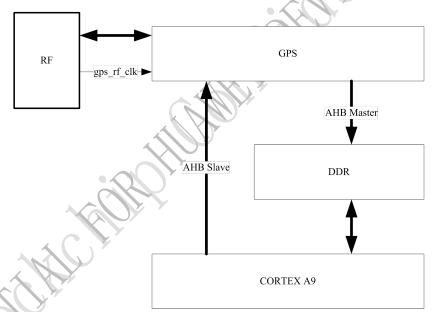

| Chapter 27 GPS                                           | $\wedge$   |

|                                                          |            |

| 27.1 Overview                                            |            |

| 27.1.1 Features                                          | 887        |

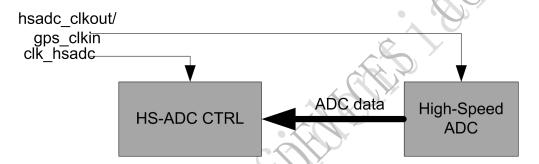

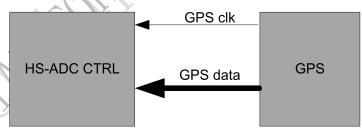

| 27.2 Block Diagram                                       | 887        |

| 27.3 Register Summary                                    | 887        |

|                                                          |            |

| 27.3.1 Base band register summary                        | 887        |

| 27.3.2 ACC operation register27.3.3 GPS Controller IOMUX | 888<br>099 |

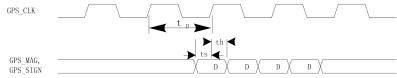

| 27.3.4 GPSTiming                                         | 900        |

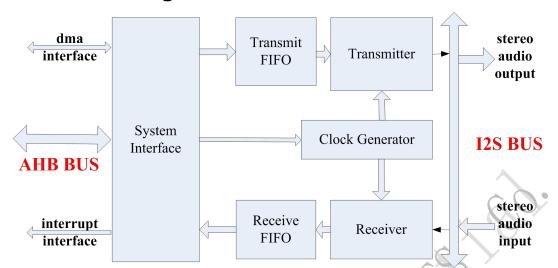

| Chapter 28 I2S/PCM Controller (2 channel)                | 890        |

| 28.1 Overview                                            | 890        |

|                                                          |            |

| 28.2 Block Diagram                                       | 891        |

| 28.3 Function description                                | 891        |

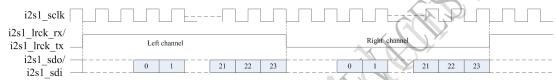

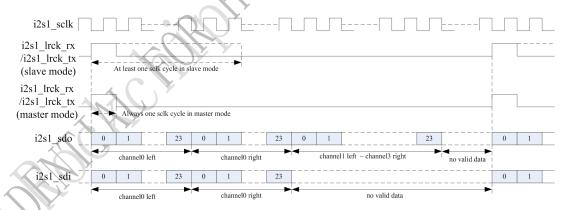

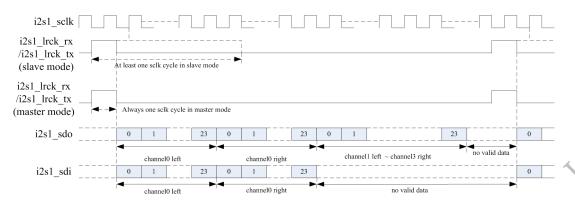

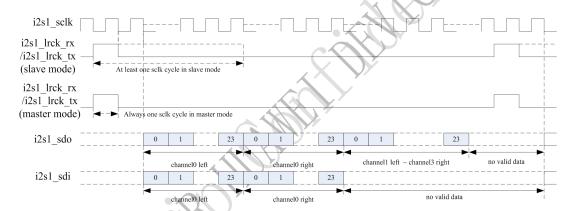

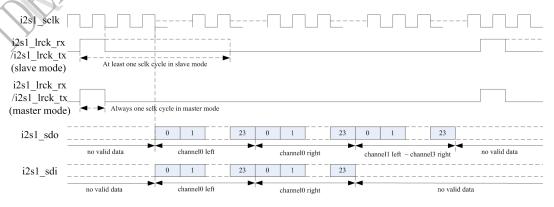

| 28.3.1 I2S normal mode                                   | 892        |

| 28.3.2 I2S left justified mode                           |            |

| 28.3.3 I2S right justified mode                          |            |

| 28.3.4 PCM early mode                                    | 893        |

| 28.3.5 PCM late1 mode                                    |            |

| 28.3.6 PCM late2 mode                                    |            |

| 28.3.7 PCM late3 mode                                    |            |

| 28.4 Register description                                | 895        |

| 28.4.1 Register Summary                                  | 895        |

| 28.4.2 Detail Register Description                       |            |

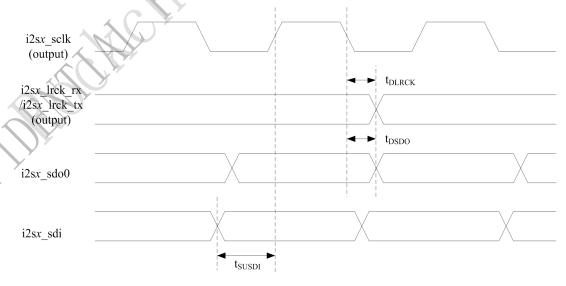

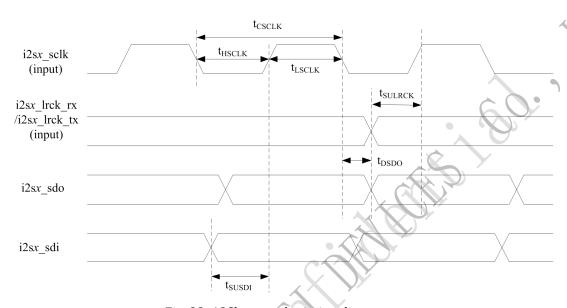

| 28.5 Timing Diagram                                      | 905        |

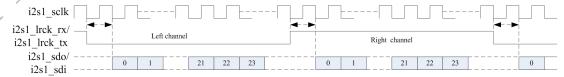

| 28.5.1 Master mode                                       | 905        |

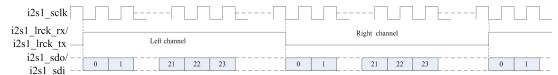

| 28.5.2 Slave mode                                        |            |

| 28.6 Interface description                               |            |

| ·                                                        |            |

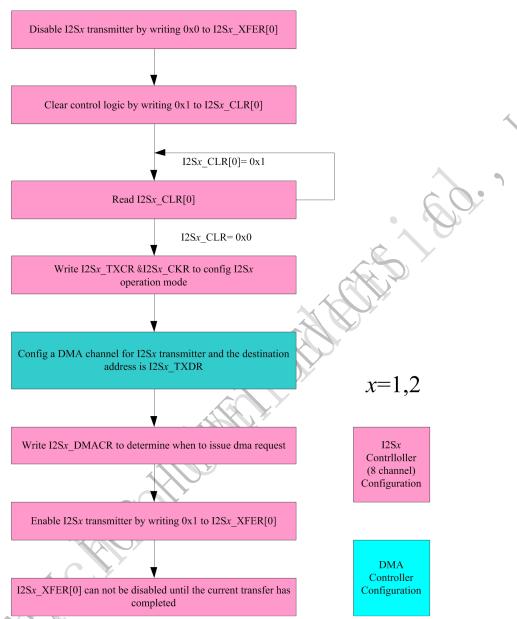

| 28.7 Application Notes                                   |            |

| Chapter 29 SPDIF transmitter                             |            |

| 29.1 Overview                                            | 909        |

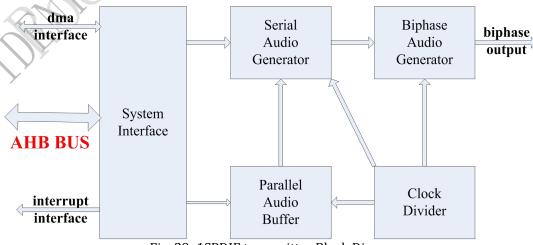

| 29.2 Block Diagram                                       | 909        |

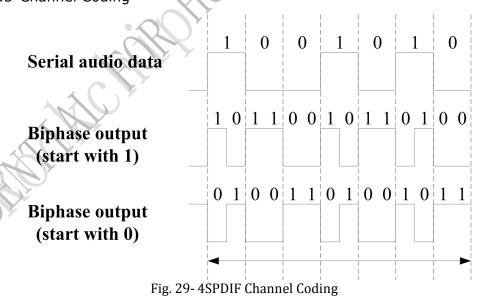

| 29.3 Function description                                                             | 910               |

|---------------------------------------------------------------------------------------|-------------------|

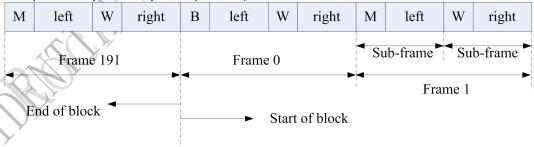

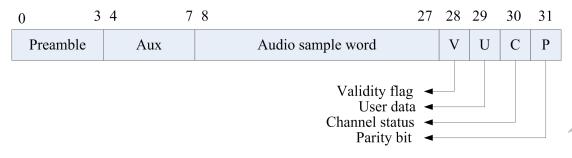

| 29.3.1 Frame Format                                                                   | 911<br>911        |

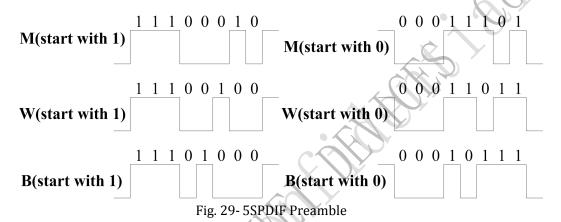

| 29.3.4 Preamble 29.4 Register description                                             |                   |

| 29.4.1 Register Summary29.4.2 Detail Register Description                             | 913               |

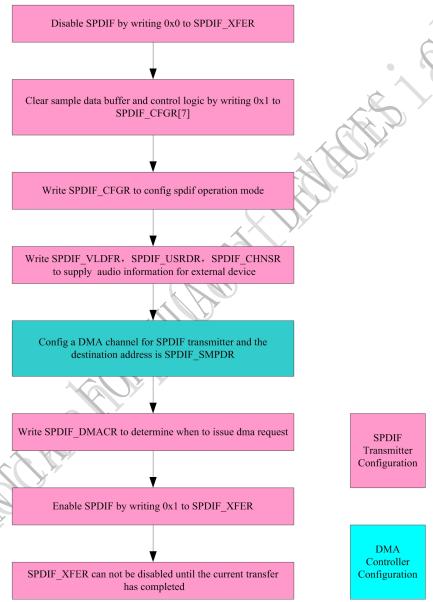

| 29.6 Application Notes                                                                | 915               |

| Chapter 30 SDIO Host Controller                                                       |                   |

| 30.2 Block Diagram                                                                    | 916               |

| 30.3 Function description                                                             |                   |

| 30.4 Register description                                                             | 917               |

| 30.5 Timing Diagram                                                                   |                   |

| 30.6 Interface description                                                            | 917               |

| 30.6.1 Card-Detect and Write-Protect Mechanism                                        | 917               |

| 30.7 Application Notes                                                                |                   |

| Chapter 31 MAC Ethernet Interface                                                     |                   |

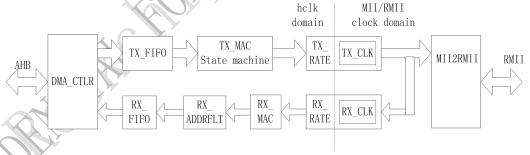

| 31.1.1 Features31.2 Block Diagram                                                     |                   |

| 31.2.1 Architecture                                                                   | 921               |

| 31.2.4 Mangement Interface                                                            |                   |

| 31.3.1 Register Summary                                                               | 923               |

| 31.4 Timing Diagram                                                                   |                   |

| 31.5 Interface Description                                                            |                   |

| 31.6 Application Notes                                                                |                   |

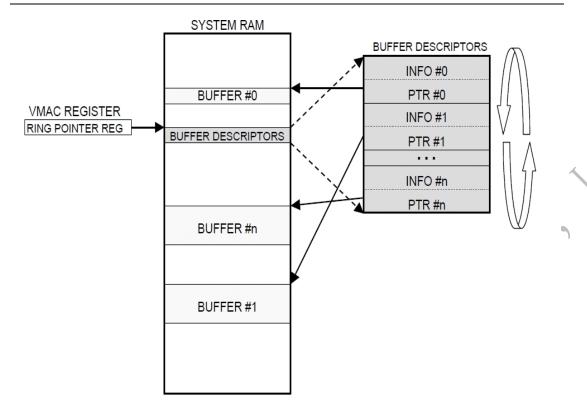

| 31.6.1 Buffer Descriptors                                                             | 936<br>938<br>940 |

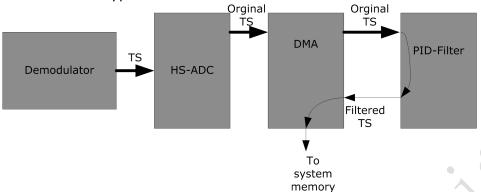

| 31.6.5 Automatic Descriptor Polling<br>Chapter 32 High-Speed ADC /TS stream Interface |                   |

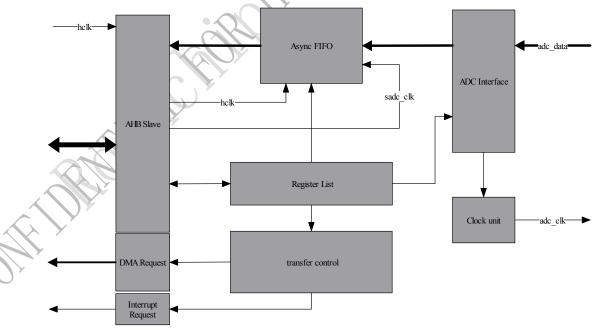

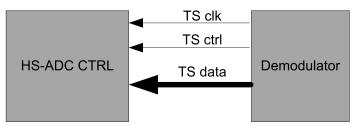

| 32.1 Overview                                          | 942        |

|--------------------------------------------------------|------------|

| 32.1.1 Features                                        | 942        |

| 32.2 Block Diagram                                     | 942        |

| 32.3 Function Description                              | 943        |

| 32.4 Register Description                              | 944        |

|                                                        | 944        |

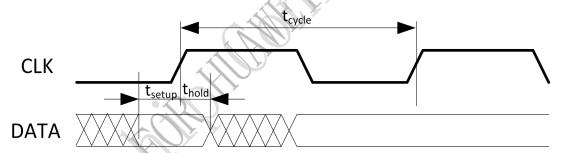

| 32.4.2 Detail Register Description 32.5 Timing Diagram | 944<br>948 |

| 32.6 Interface Description                             | A          |

|                                                        |            |

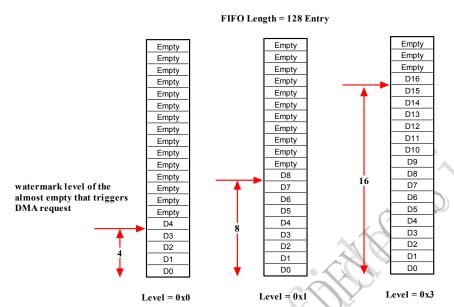

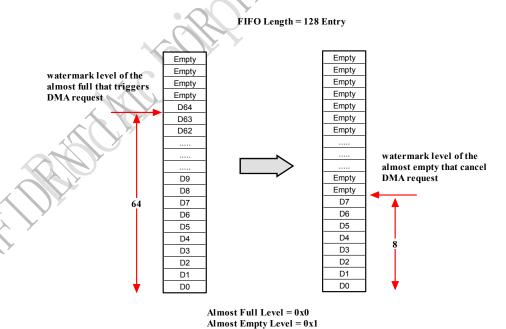

| 32.7 Application Notes                                 |            |

| Chapter 33 PID-FILTER33.1 Overview                     |            |

|                                                        | 952        |

| 33.1.1 Key Feature                                     |            |

| 33.3 Function Description                              |            |

| 33.4 Register Description                              |            |

|                                                        |            |

| 33.4.1 Register summary                                | 953        |

| 33.4.2 Register description                            | 955        |

|                                                        | 956        |

| 33.5.2 About internal buffer access                    | 956        |

|                                                        | 956        |

| 34.1 Overview                                          |            |

| 34.2 Block Diagram                                     | 957        |

| 34.3 Function description                              |            |

| 34.4 Register description                              |            |

|                                                        |            |

|                                                        | 961<br>961 |

| 34.5 Timing Diagram                                    |            |

| 34.6 Interface description                             | 969        |

| 34.7 Application Notes                                 | 970        |

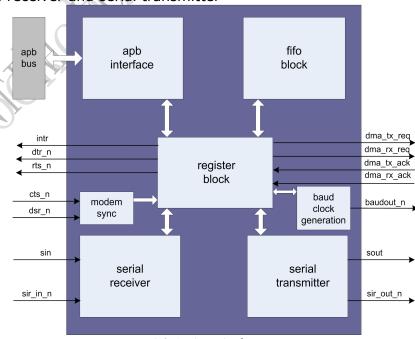

| Chapter 35 UART Interface                              | 972        |

| 35.1 Overview                                          |            |

| 35.1.1 Features                                        | 972        |

| 35.2 Block Diagram                                     | 972        |

| 35.3 Function description                              | 973        |

|                                                        |            |

| 35.4 Register description                                     | 976  |

|---------------------------------------------------------------|------|

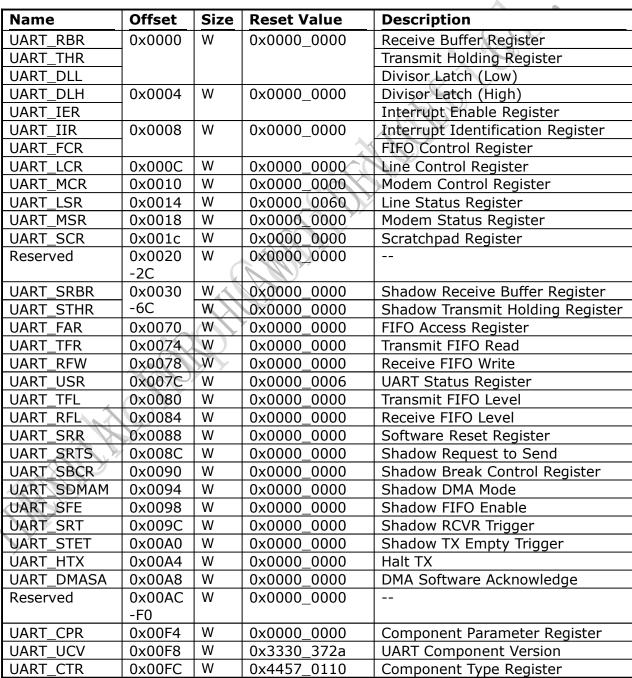

| 35.4.1 Registers Summary                                      |      |

| 35.4.2 Registers detail description35.5 Interface description |      |

| ·                                                             |      |

| 35.6 Application Notes                                        |      |

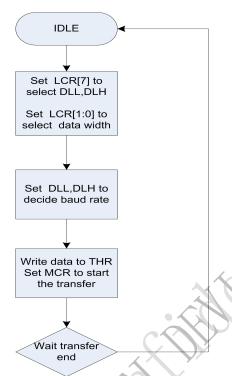

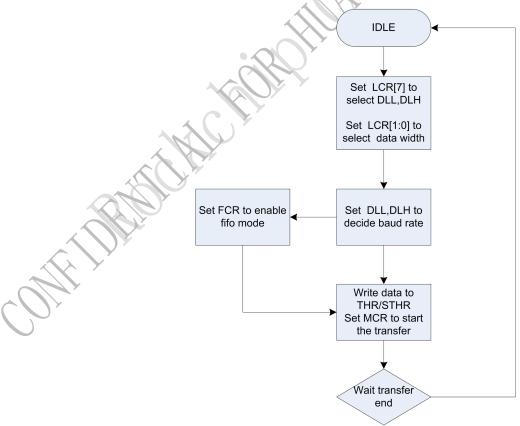

| 35.6.1 None FIFO Mode Transfer Flow                           |      |

| 35.6.3 Baud Rate Calculation                                  |      |

| Chapter 36 I2C Interface                                      |      |

| 36.1 Overview                                                 | 992  |

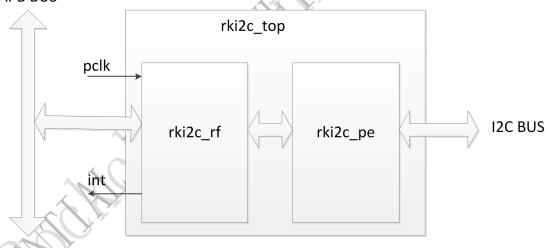

| 36.2 Block Diagram                                            | 992  |

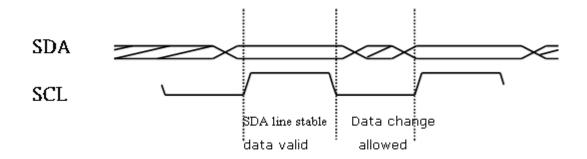

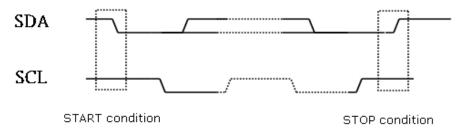

| 36.3 Function description                                     | 993  |

| 36.4 Register description                                     | 996  |

| 36.5 Timing Diagram                                           | 1003 |

| 36.6 Interface description                                    | 1003 |

| 36.7 Application Notes                                        | 1004 |

| Chapter 37 GPIO                                               | 1009 |

| 37.1 Overview                                                 |      |

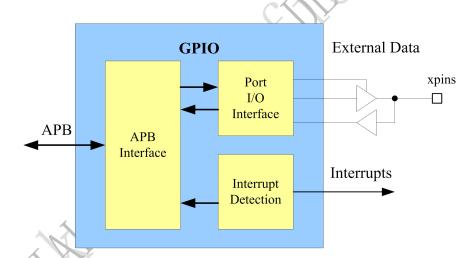

| 37.2 Block Diagram                                            |      |

| 37.3 Function description                                     |      |

|                                                               |      |

| 37.3.1 Operation37.3.2 Programming                            |      |

| 37.4 Register description                                     |      |

| 37.4.1 Registers Summary                                      | 1011 |

| 37.4.2 Detail Register Description                            | 1012 |

| Chapter 38 Timer                                              |      |

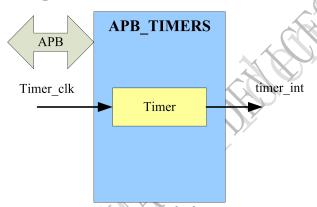

| 38.1 Overview                                                 | 1015 |

| 38.2 Block Diagram                                            | 1015 |

| 38.3 Function description                                     | 1015 |

| 38.3.1 Timer clk selection                                    | 1015 |

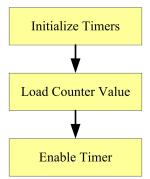

| 38.3.2 Programming sequence                                   |      |

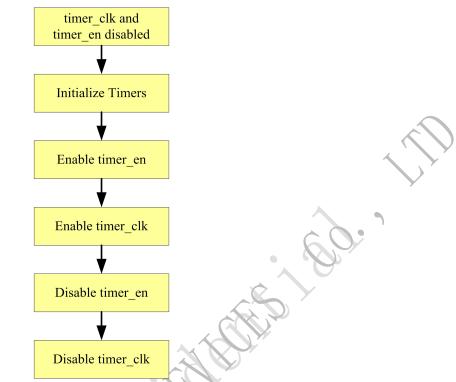

| 38.3.3 Enabling and Disabling a Timer                         |      |

| 38.3.4 Loading a Timer Countdown Value                        |      |

|                                                               |      |

| 38.4.1 Registers Summary38.4.2 Detail Register Description    |      |

| 38.5 Application Notes                                        |      |

|                                                               |      |

| Chapter 39 PWM                                                |      |

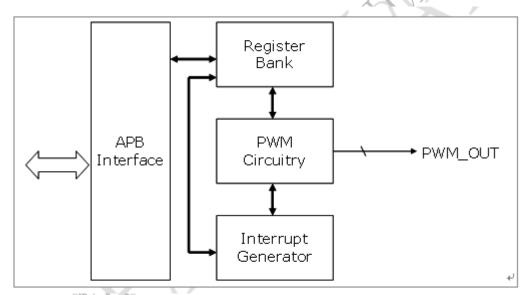

| 39.1 Overview                                                 |      |

| 39.1.1 Features39.2 Block Diagram                                                   |                      |

|-------------------------------------------------------------------------------------|----------------------|

| 39.3 Register description                                                           | 1021                 |

| 39.3.1 Register Summary39.3.2 Detail Register Description39.4 Interface description | 1022                 |

| Chapter 40 WatchDog40.1 Overview                                                    |                      |

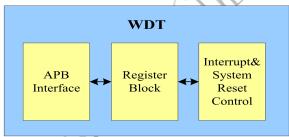

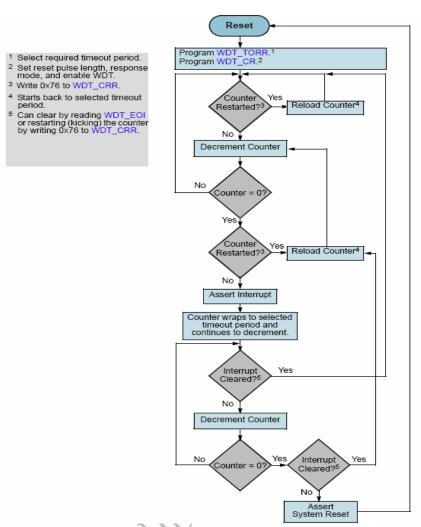

| 40.2 Block Diagram                                                                  | 1025                 |

| 40.3 Function Description                                                           |                      |

| 40.3.1 Operation 40.3.2 Programming sequence 40.4 Register description              | 1026<br>1027         |

| 40.4.1 Register Summary                                                             | 1027<br>1027<br>1031 |

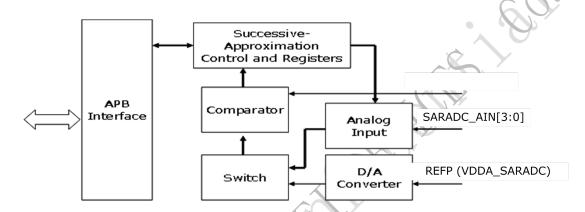

| 41.2 Block Diagram                                                                  |                      |

| 41.3 Function Description                                                           | 1031                 |

| 41.4 Register description                                                           | 1032                 |

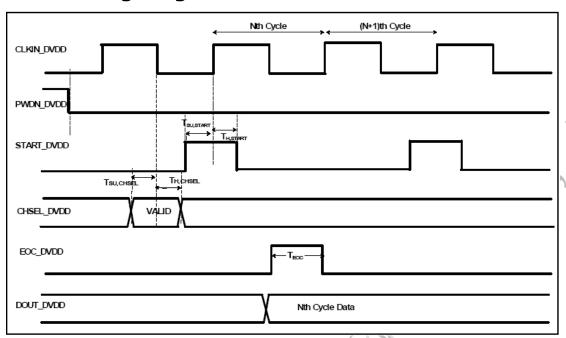

| 41.4.1 Register Summary                                                             | 1032                 |

| 41.6 Application Notes                                                              | 1034                 |

| Chapter 42 eFuse42.1 Overview                                                       |                      |

| Chapter 43 Chip Test Solution                                                       |                      |

### **Figure Index**

| Fig. 1-1 RK3168 Block Diagram                                              | 39  |

|----------------------------------------------------------------------------|-----|

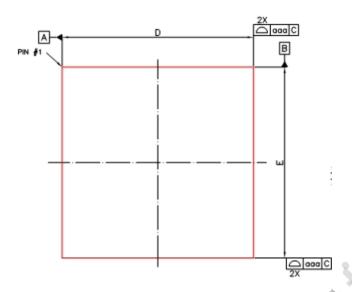

| Fig. 1-2 RK3168 TFBGA453 Package Top View                                  | 57  |

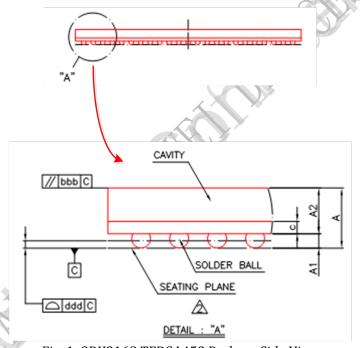

| Fig. 1-3 RK3168 TFBGA453 Package Side View                                 | 57  |

| Fig. 1-4 RK3168 TFBGA453 Package Bottom View                               | 58  |

| Fig. 1-5 RK3168 TFBGA453 Package Dimension                                 | 58  |

| Fig. 1-6 RK3168 Ball Mapping Diagram                                       | 60  |

| Fig. 1-7 External Reference Circuit for 24MHzOscillators                   |     |

| Fig. 1-8 External reference circuit for PLL                                |     |

| Fig. 1-9 RK3168 USB OTG/Host2.0 interface reference connection             |     |

| Fig. 1-10 RK3168 reset signals sequence                                    |     |

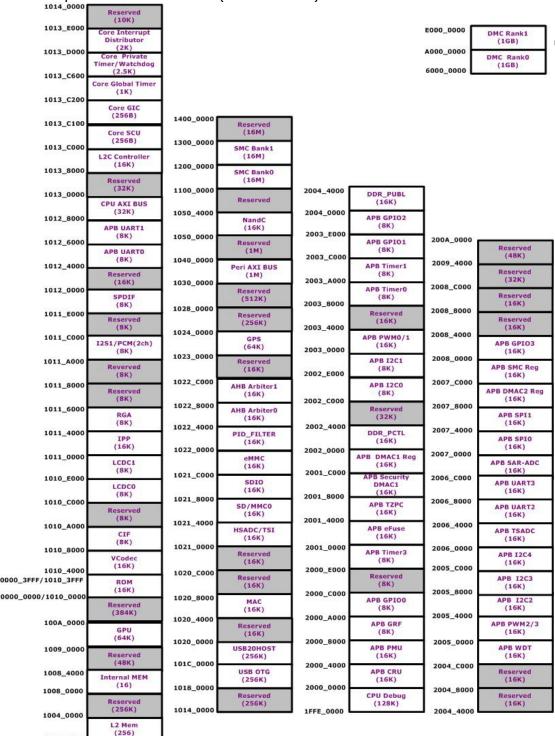

| Fig. 2-1 RK3168 Address Mapping before remap                               |     |

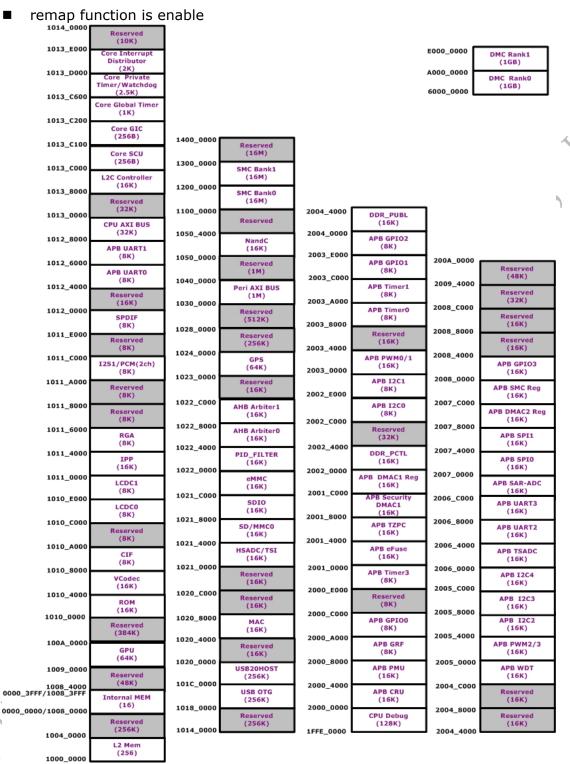

| Fig. 2-2 RK3168 Address Mapping after remap                                |     |

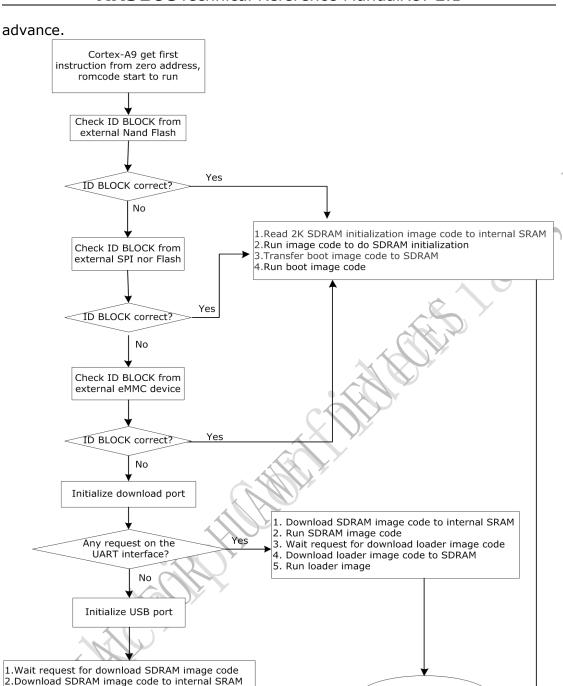

| Fig. 2-3 RK3168 boot procedure flow                                        |     |

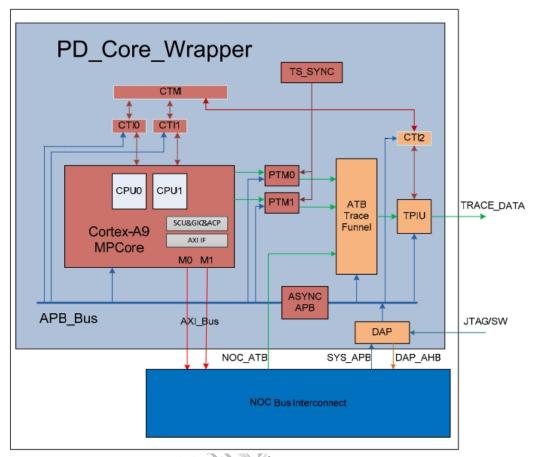

| Fig. 6-1 RK3168 Debug system structure                                     | 88  |

| Fig. 6-2 DAP SWJ interface                                                 |     |

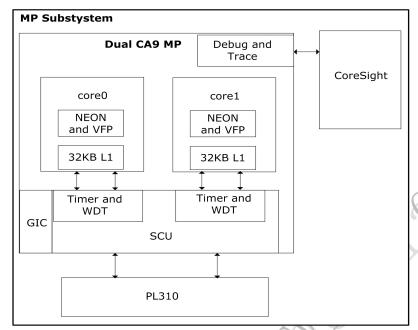

| Fig. 8-1 MP Subsystem architecture                                         |     |

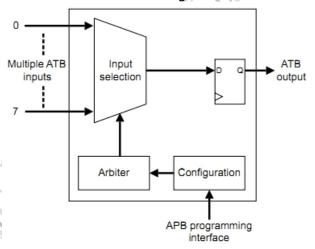

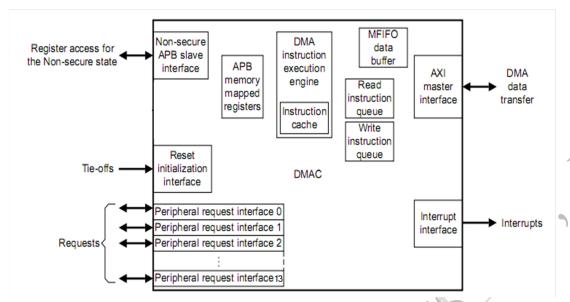

| Fig. 10-1 Block diagram of dmac0                                           | 274 |

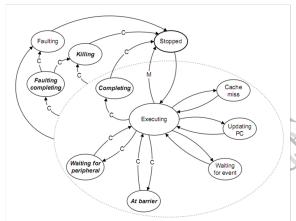

| Fig. 10-2 DMAC0 operation states                                           |     |

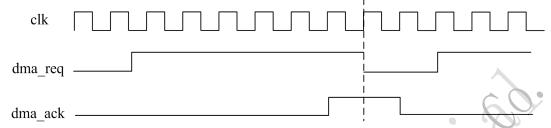

| Fig. 10-3 DMAC0 request and acknowledge timing                             |     |

| Fig. 11-1 Block diagram of dmac1                                           | 301 |

| Fig. 11-1 Block diagram of dmac1Fig. 12-1 Block diagram of GIC             | 319 |

| Fig. 12-2 GIC Interrupt handling state machine                             |     |

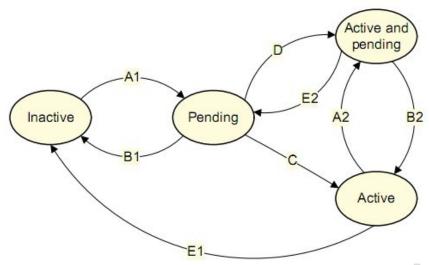

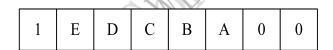

| Fig. 12-3 Secure view of the priority field for a Secure interrupt         |     |

| Fig. 12-4 Non-secure view of the priority field for a Non-secure interrupt |     |

| Fig. 12-5 Secure read of the priority field for a Non-secure interrupt     |     |

| Fig. 13-1 Protocol controller architecture                                 |     |

| Fig. 13-2 PHY controller architecture                                      |     |

| Fig. 13-3 Protocol controller architecture                                 |     |

| Fig. 13-4 DDR PHY architecture                                             |     |

| -                                                                          |     |

| Fig. 13-5 DDR PHY master DLL architecture diagram                          |     |

| Fig. 13-6 DDR PHY master-slave DLL architecture diagram                    |     |

| Fig. 13-7 Strobe Gating Requirements During Read Operations                |     |

| Fig. 13-8 DQS gating – passive windowing mode                              |     |

| Fig. 13-9 DQS gating – active windowing mode                               |     |

| Fig. 13-10 DDR3 burst write operation: AL=0,CWL=4, BC4                     |     |

| Fig. 13-11 DDR3 burst read operation: AL=0,CL=5, BC4                       |     |

| Fig. 13-12 LPDDR2 burst write operation: WL=1,BL=4                         |     |

| Fig. 13-13 LPDDR2 burst read operation: RL=3, BL=4                         |     |

| Fig. 13-14 Protocol controller architecture                                |     |

| Fig. 13-15 DLL reset requirements                                          |     |

| Fig. 13-16 DLL reset requirements                                          |     |

| Fig. 13-17 Impedance Calibration Circuit                                   |     |

| Fig. 13-18 I/O cell arrangement with retention                             |     |

| Fig. 13-19 Sequence of Events to Enter and Exit Retention                  |     |

| Fig. 14-1 SMC architecture diagram                                         |     |

| Fig. 14-2 Software Mechanism of Direct Commands in SMC                     |     |

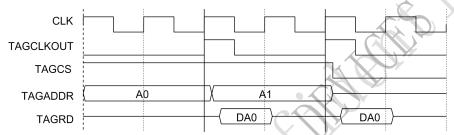

| Fig. 14-3 SMC asynchronous read timing                                     |     |

| Fig. 14-4 SMC asynchronous read timing in multiplexed mode                 |     |

| Fig. 14-5 SMC asynchronous write timing                                    |     |

| Fig. 14-6 SMC asynchronous write timing in multiplexed mode 1              |     |

| Fig. 14-7 SMC asynchronous write timing in multiplexed mode 2              |     |

| Fig. 14-8 SMC page read timing                                             | 584 |

|      | 14-9 SMC timing diagram of asynchronous read                |            |

|------|-------------------------------------------------------------|------------|

| Fig. | 14-10 Asynchronous Write Timing Diagram In Multiplexed Mode | 594        |

| Fig. | 17-1 SD/MMC Controller Block Diagram                        | 600        |

| Fig. | 17-2 SD/MMC Card-Detect Signal                              | 604        |

| Fig. | 17-3 SD/MMC Command Path State Machine                      | 606        |

| _    | 17-4 SD/MMC Data Transmit State Machine                     |            |

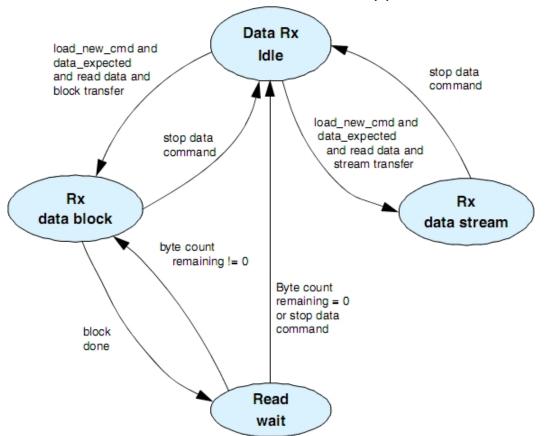

| _    | 17-5 SD/MMC Data Receive State Machine                      |            |

| _    | 17-6 Card-Detect and Write-Protect                          |            |

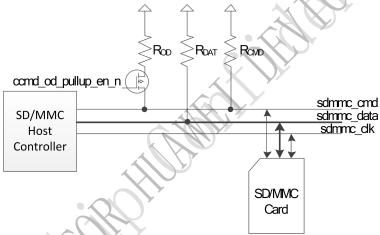

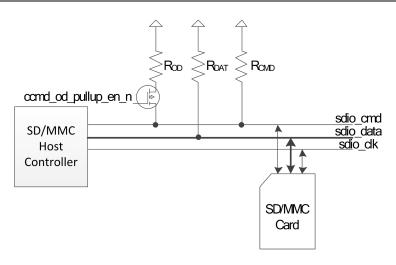

|      | 17-7 SD/MMC Termination                                     |            |

|      | 17-8 Initialization Sequence                                |            |

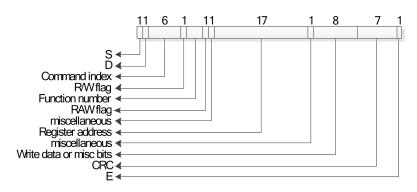

|      | 17-9 Command format for CMD52                               |            |

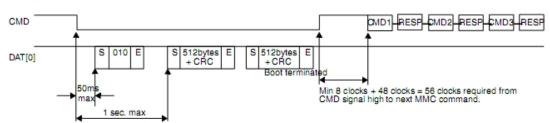

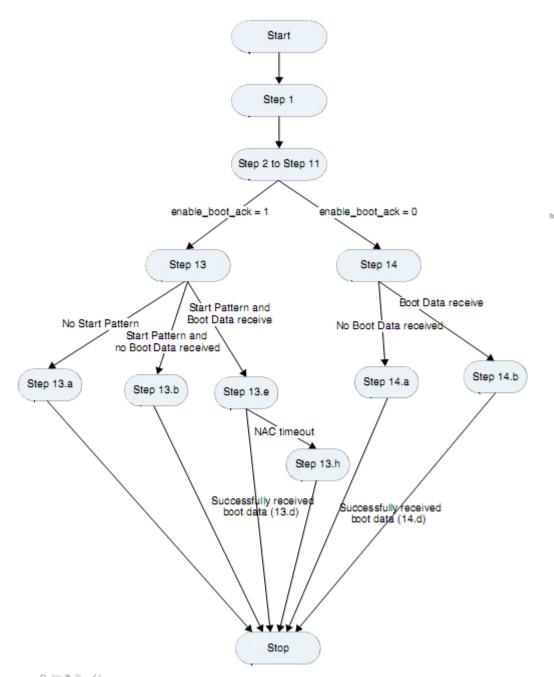

|      | 17-10 Boot Operation                                        |            |

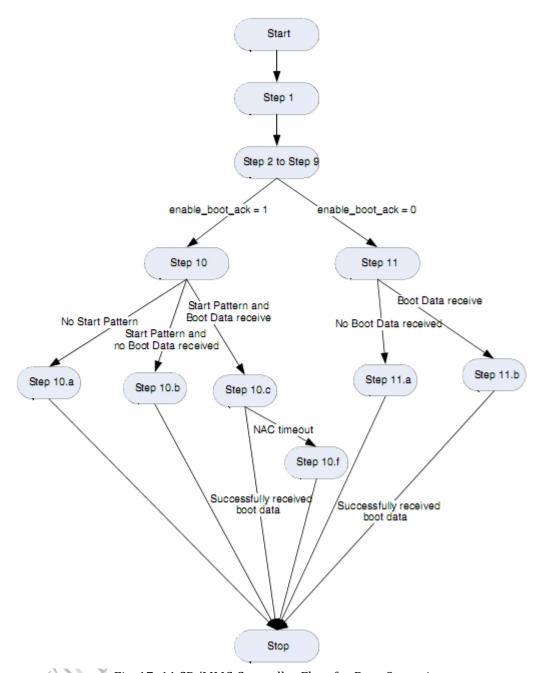

|      | 17-11 SD/MMC Controller Flow for Boot Operation             |            |

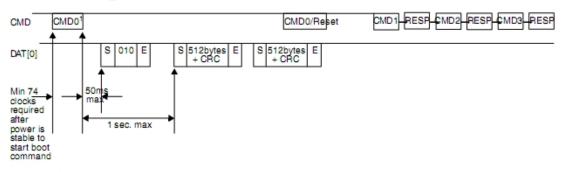

|      | 17-12 Alternative Boot Opertation                           |            |

|      | 17-13 Host Controller Flow for Alternative Boot Mode        |            |

| _    | 17-14 Voltage Switching Command Flow Diagram                |            |

|      | 17-15 ACMD41 Argument                                       |            |

| Fig. | 17-16 ACMD41 Response(R3)                                   | 664        |

| Fig. | 17-17 Voltage Switch Normal Scenario                        | 664        |

|      | 17-17 Voltage Switch Normal Scenario                        |            |

| Fig. | 18-1 Embedded SRAM block diagram                            | 668        |

| Fig. | 22. 1 LCDC Block Diagram                                    | 674        |

| rig. | 22-1 LCDC Block Diagram22-2 LCDC Dual LCDCs in SOC          | 074<br>674 |

| rig. | 22-3 LCDC Frame Buffer Data Format                          | 0/4<br>675 |

| Fig. | 22-3 LCDC Fidille Bullet Data Fulfildt                      | 675        |

| Fig. | 22-4 LCDC Win2 Palette (8bpp/4bpp)22-5 LCDC Hwc Data Format | 676        |

| rig. | 22-6 LCDC Virtual Display Mode                              | 0/0        |

| rig. | 22-6 LCDC VIRUAL DISPIRA MODE                               | 6//        |

| _    | 22-7 LCDC Scaling Down Offset                               |            |

| _    | 22-8 LCDC Scaling Up Offset                                 |            |

|      | 22-9 LCDC Interlace Vertical Filtering                      |            |

|      | 22-10 LCDC Overlay Block Diagram                            |            |

|      | 22-11 LCDC Overlay Display                                  |            |

| _    | 22-12 LCDC Transparency Color Key                           |            |

|      | 22-13 LCDC Alpha blending                                   |            |

|      | 22-14 LCDC Replication                                      |            |

| _    | 22-15 LCDC Dithering                                        |            |

| _    | 22-16 LCDC RGB interface timing                             |            |

| _    | 22-17 LCDC MCU interface (i80)timing                        |            |

|      | 22-18 LCDC RGB interface timing setting                     |            |

| _    | 22-19 LCDC Serail RGB LCD interface                         |            |

| _    | 22-20 LCDC MCU interface timing setting                     |            |

|      | 22-21 LCDC RGB delta LCD interface                          |            |

| _    | 24-1 CIF block diagram                                      |            |

| _    | 24-2 Timing diagram for CIF when vsync low active           |            |

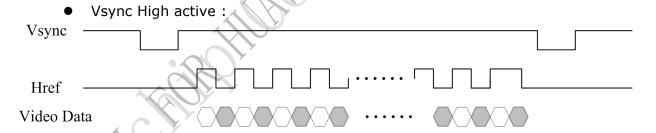

|      | 24-3 Timing diagram for CIF when vsync high active          |            |

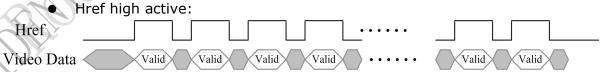

| _    | 24-4 Timing diagram for CIF when href high active           |            |

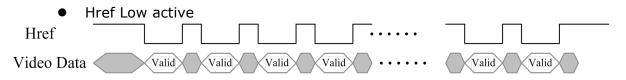

|      | 24-5 Timing diagram for CIF when href low active            |            |

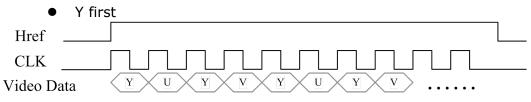

|      | 24-6 Timing diagram for CIF when Y data first               |            |

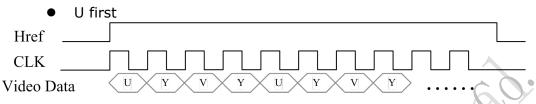

| Fig. | 24-7 Timing diagram for CIF when U data first               | 708        |

|      | 24-8 CCIR656 timing                                         |            |

| Fig. | 24-9 Raw Data or JPEG Timing                                | 708        |

|      | 25-1 USB HOST 2.0 Architecture                              |            |

| Fig. | 25-2 USB HOST 2.0 Controller Architecture                   | 727        |

| _    | 25-3 USB HOST 2.0 PHY Architecture                          |            |

| Fig. | 26-1 USB OTG 2.0 Architecture                                      | 734  |

|------|--------------------------------------------------------------------|------|

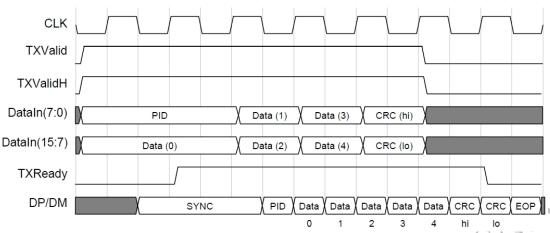

| Fig. | 26-2 UTMI interface -Transmit timing for a data packet             | 736  |

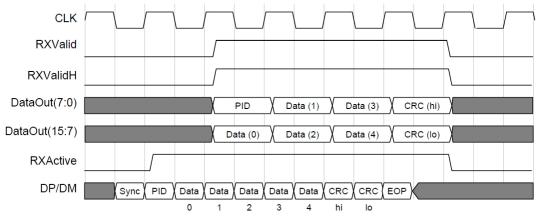

|      | 26-3 UTMI interface - Receive timing for a data packet             |      |

|      | 26-4 USB OTG2.0 Controller Architecture                            |      |

| _    | 26-5 USB OTG2.0 Controller - Host Architecture                     |      |

| _    | 26-6 USB OTG2.0 Controller - Host Architecture                     |      |

|      | 26-7 USB OTG2.0 Controller – Internal DMA mode                     |      |

|      | 26-8 USB OTG 2.0 Controller host mode FIFO address mapping         |      |

|      | 26-9 USB OTG 2.0 Controller device mode FIFO address mapping       |      |

|      | 26-10 USB OTG 2.0 Controller Packet FIFO controller                |      |

| _    | 26-11 DFIFO single-port synchRnous SRAM interface                  |      |

| _    | 26-12 USB OTG 2.0 Controller – MAC block diagram                   |      |

| _    | 26-13 USB OTG 2.0 PHY Architecture                                 |      |

| _    | 26-14 USB OTG 2.0 PHY power supply and power up sequency           |      |

|      | 28-1 GPS block diagram                                             |      |

|      | 28-2 GPS timing waveform                                           |      |

|      |                                                                    |      |

| rig. | 29-1 I2S/PCM1/2 controller (2 channel) Block Diagram               | 094  |

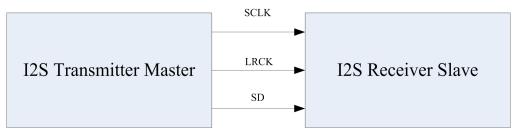

| _    | 29-2 I2S transmitter-master & receiver-slave condition             |      |

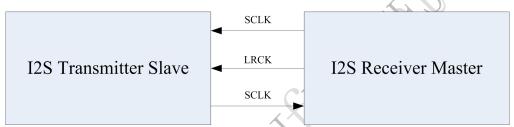

| _    | 29-3 I2S transmitter-slave & receiver-master condition             |      |

| rig. | 29-4 I2S normal mode timing format                                 | 895  |

| rig. | 29-5 I2S left justified mode timing format                         | 896  |

| Fig. | 29-6 I2S right justified mode timing format                        | 896  |

| Fig. | 29-7 PCM early mode timing format                                  | 896  |

| Fig. | 29-8 PCM late1 mode timing format29-9 PCM late2 mode timing format | 897  |

| Fig. | 29-9 PCM late2 mode timing format                                  | 89 / |

|      | 29-10 PCM late3 mode timing format                                 |      |

|      | 29-11 Master mode timing diagram                                   |      |

| _    | 29-12 Slave mode timing diagram                                    |      |

| _    | 29-13 I2S/PCM1/2 controller transmit operation flow chart          |      |

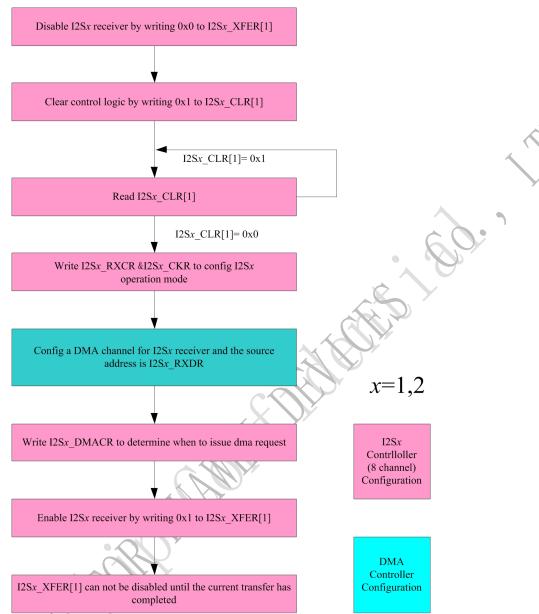

|      | 29-14 I2S/PCM1/2 controller receive operation flow chart           |      |

|      | 30-1 SPDIF transmitter Block Diagram                               |      |

|      | 30-2 SPDIF Frame Format                                            |      |

| _    | 30-3 SPDIF Sub-frame Format                                        |      |

| _    | 30-4 SPDIF Channel Coding                                          |      |

|      | 30-5 SPDIF Preamble                                                |      |

| Fig. | 30-6 SPDIF transmitter operation flow chart                        | 918  |

|      | 31-1 SD/MMC Controller Block Diagram                               |      |

| Fig. | 31-2 Card-Detect and Write-Protect                                 | 920  |

| Fig. | 31-3 SD/MMC Termination                                            | 921  |

| Fig. | 32-1 VMAC architecture                                             | 923  |

| Fig. | 32-2 VMAC Frame structure                                          | 924  |

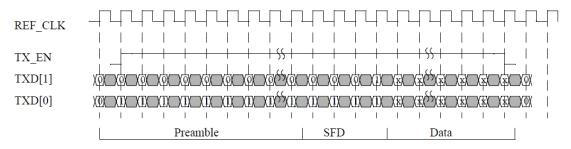

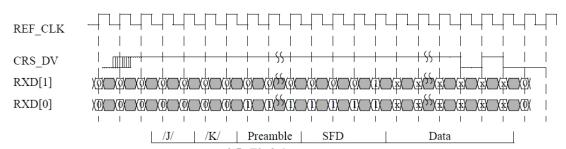

| Fig. | 32-3 RMII transmission in 100Mb/s mode                             | 925  |

| Fig. | 32-4 RMII reception with no errors in 100Mb/s mode                 | 925  |

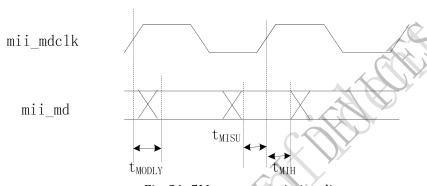

|      | 32-5 Management timing diagram                                     |      |

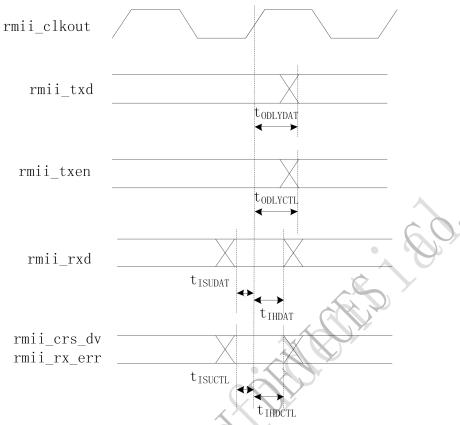

| Fig. | 32-6 RMII timing diagram                                           | 937  |

| _    | 32-7 VMAC buffer chain                                             |      |

|      | 32-8 VMAC transmit buffer descriptor written by CPU                |      |

|      | 32-9 VMAC transmit buffer descriptor written by VMAC               |      |

|      | 32-10 VMAC receive buffer descriptor written by VMAC               |      |

|      | 32-11 VMAC receive buffer descriptor written by CPU                |      |

|      | 33-1 HS-ADC/TS Interface block diagram                             |      |

| _    | 33-2 HS-ADC application diagram                                    |      |

| _    | 33-3 GPS application diagram                                       |      |

| _    | 33-4 TS application diagram                                        |      |

| 4 .  | application araqualiticon                                          |      |

| Fig. | 33-5 HS-AD Interface timing diagram                                | 951   |

|------|--------------------------------------------------------------------|-------|

| Fig. | 33-6 Almost empty triggers a DMA request by DMA request mode       | 953   |

|      | 33-7 Almost full triggers a DMA request by DMA request mode        |       |

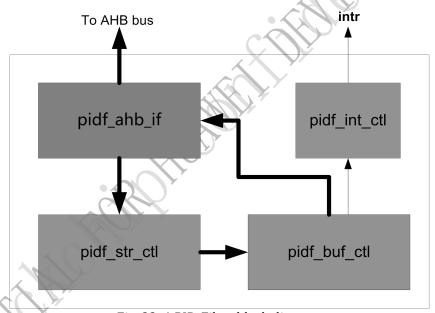

| Fig. | 34-1 PID-Filter block diagram                                      | 955   |

| Fig. | 34-2 PID-Filter data flow                                          | 959   |

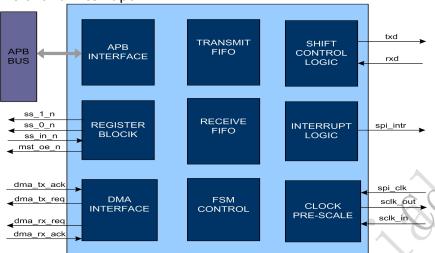

| Fig. | 35-1 SPI Controller Block diagram                                  | 961   |

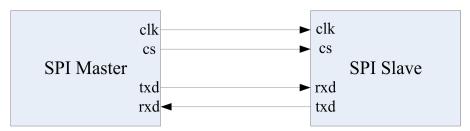

| Fig. | 35-2 SPI Master & Slave Interconnection                            | 962   |

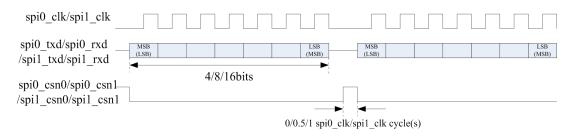

| Fig. | 35-3 SPI Format (SCPH=0 SCPOL=0)                                   | 963   |

| Fig. | 35-4 SPI Format (SCPH=0 SCPOL=1)                                   | 963   |

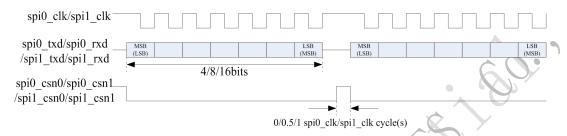

| Fig. | 35-5 SPI Format (SCPH=1 SCPOL=0)                                   | 963   |

| Fig. | 35-6 SPI Format (SCPH=1 SCPOL=1)                                   | 963   |

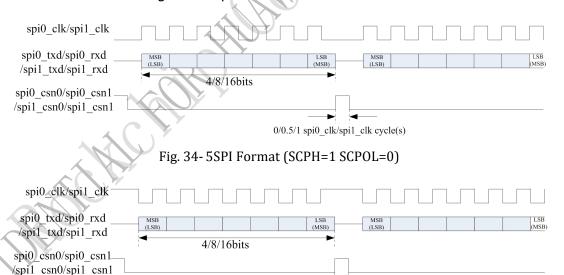

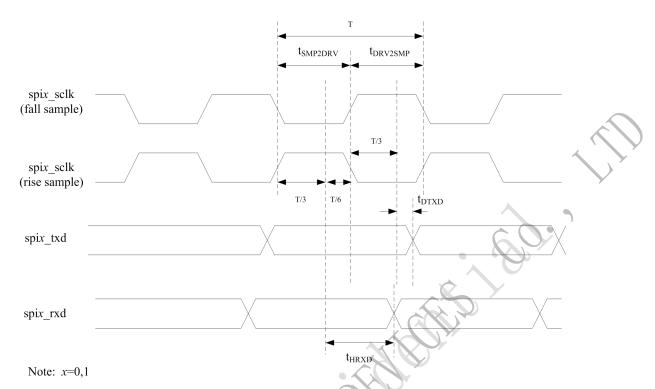

|      | 35-7 SPI controller timing diagram                                 |       |

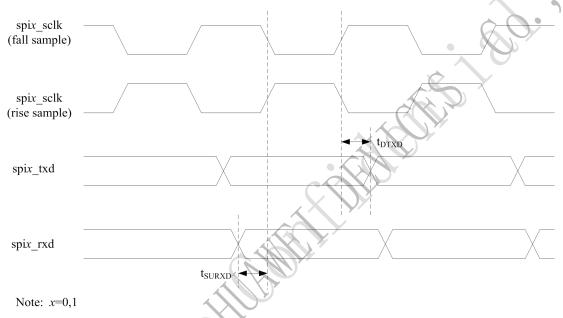

| Fig. | 35-8 SPI controller timing diagram in slave mode                   | 972   |

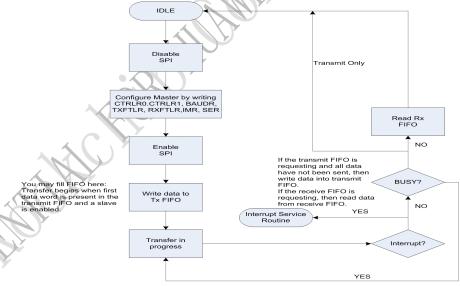

| Fig. | 35-9 SPI Master transfer flow diagram                              | 973   |

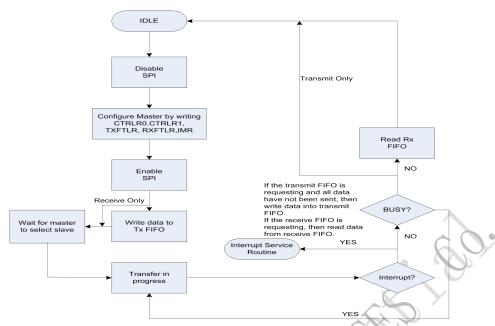

| Fig. | 35-10 SPI Slave transfer flow diagram                              | 974   |

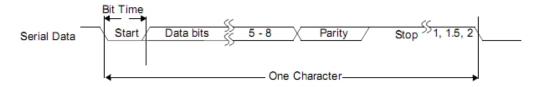

|      | 36-1 UART Architecture                                             |       |

|      | 36-2 UART Serial protocol                                          |       |

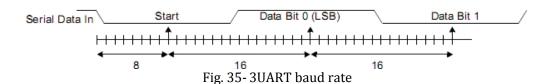

|      | 36-3 UART baud rate                                                |       |

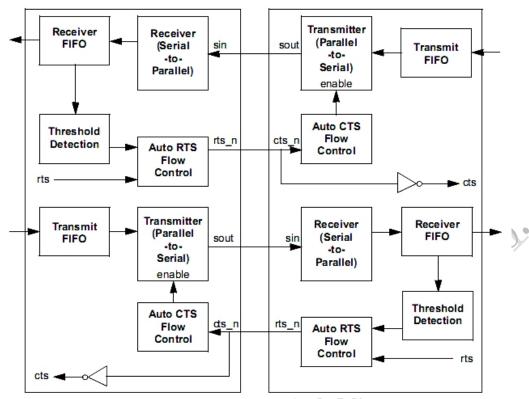

| Fig. | 36-4 UART Auto flow control block diagram                          | 978   |

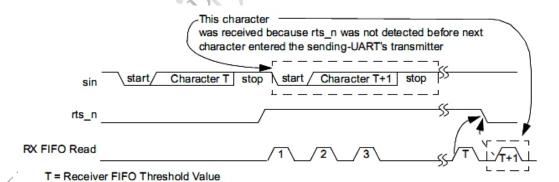

| Fig. | 36-5 UART AUTO RTS TIMING                                          | 978   |

| Fig. | 36-6 UART AUTO CTS TIMING                                          | 979   |

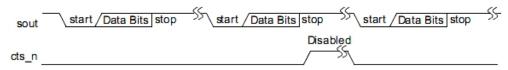

| Fig. | 36-7 UART none fifo mode                                           | 992   |

| Fig. | 36-8 UART fifo mode                                                | 992   |

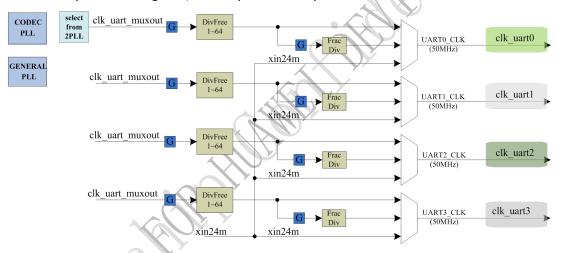

| Fig. | 36-9 UART clock generation37-1 I2C architechture                   | 993   |

| Fig. | 37-1 I2C architechture                                             | 995   |

|      | 37-2 I2C DATA Validity                                             |       |

|      | 37-3 I2C Start and stop conditions                                 |       |

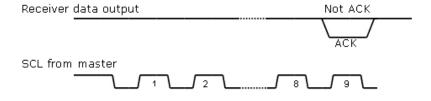

| Fig. | 37-4 I2C Acknowledge                                               | 998   |

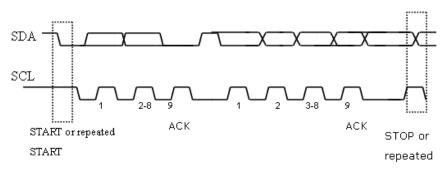

| Fig. | 37-5 I2C byte trasnfer                                             | 999   |

|      | 37-6 I2C timing diagram                                            |       |

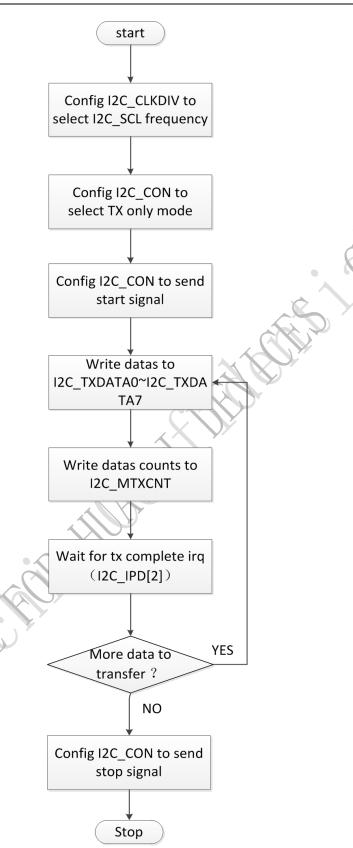

| _    | 37-7 I2C Flow chat for tx only mode                                |       |

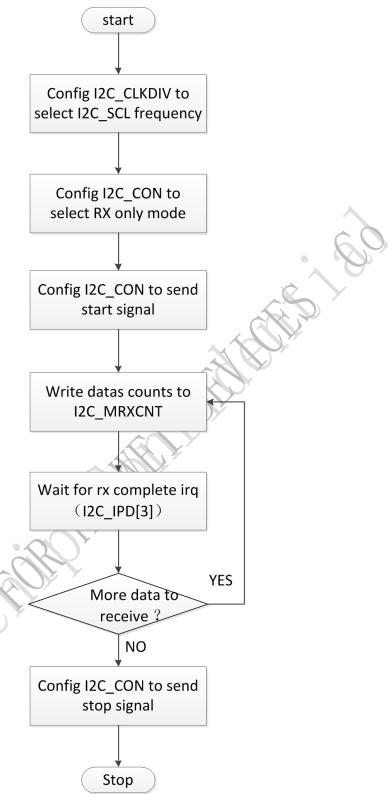

|      | 37-8 I2C Flow chat for rx only mode                                |       |

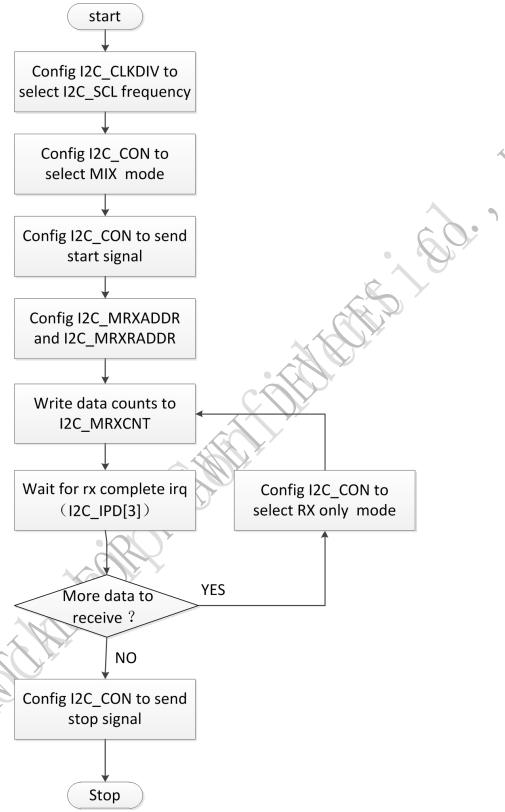

| _    | 37-9 I2C Flow chat for mix mode                                    |       |

|      | 38-1 GPIO block diagram                                            |       |

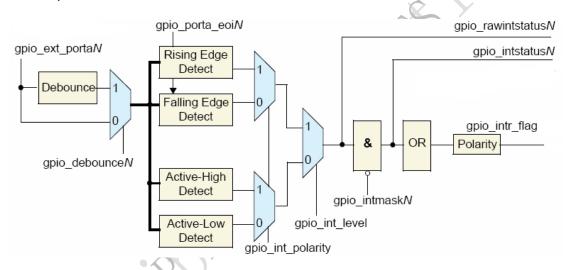

|      | 38-2 Interrupt RTL Block Diagram                                   |       |

|      | 39-1 Timer Block Diagram                                           |       |

| _    | 39-2 Timer Usage Flow                                              |       |

|      | 39-3 Timing of Timer_en and Timer_clk (timer_clk is async to pclk) |       |

|      | 39-4 Timer0 and Timer1 Usage Flow                                  |       |

| _    | 40-1 PWM architecture                                              |       |

|      | 41-1 WDT block diagram                                             |       |

|      | 41-2 WDT Operation Flow                                            |       |

|      | 42-1 RK3168 SAR-ADC block diagram                                  |       |

| Fig. | 42-2 SAR-ADC timing diagram in single-sample conversion mode       | .1042 |

### **Table Index**

| Table 1-1 RK3168 Power/Ground IO informations                          | 39  |

|------------------------------------------------------------------------|-----|

| Table 1-2RK3168 IO descriptions                                        | 42  |

| Table 1-3 RK3168 IO function description list                          | 50  |

| Table 1-4 RK3168 IO Type List                                          | 56  |

| Table 1-5RK3168Ball Pin Number Order Information                       |     |

| Table 1-6 RK3168 absolute maximum ratings                              |     |

| Table 1-7 RK3168 recommended operating conditions                      |     |

| Table 1-8 RK3168 DC Characteristics                                    |     |

| Table 1-9 Recommended operating frequency for PD_ALIVE domain          |     |

| Table 1-10 Recommended operating frequency for A9 core                 |     |

| Table 1-11 Recommended operating frequency for PD_CPU domain           | 70  |

| Table 1-12 Recommended operating frequency for PD_PERI domain          |     |

| Table 1-13 Recommended operating frequency for PD_VIO domain           |     |

| Table 1-14 Recommended operating frequency PD_GPU domain               |     |

| Table 1-15 Recommended operating frequency for PD_VIDEO domain         |     |

| Table 1-16 RK3168 Electrical Characteristics for Digital General IO    |     |

| Table 1-17 RK3168 Electrical Characteristics for PLL                   |     |

| Table 1-18 RK3168 Electrical Characteristics for SAR-ADC               | 74  |

| Table 1-19 RK3168 Electrical Characteristics for USB OTG/Host2.0 Inter |     |

| Table 1-21 RK3168 Electrical Characteristics for DDR IO                |     |

| Table 1-22 RK3168 Electrical Characteristics for eFuse                 |     |

| Table 1-23 Ferrite Bead Selection                                      |     |

| Table 2-1 RK3168 Interrupt connection list                             |     |

| Table 2-2 RK3168 DMAC0 Hardware request connection list                |     |

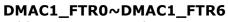

| Table 2-3 RK3168 DMAC1 Hardware request connection list                | 85  |

| Table 6-1SWJ interface                                                 |     |

| Table 6-2TPIU interface                                                |     |

| Table 10-1DMAC0 Request Mapping Table                                  |     |

| Table 10-2 DMAC Instruction sets                                       | 298 |

| Table 11-1DMAC1 Request Mapping Table                                  |     |

| Table 17-1 Bits in Interrupt Status Register                           |     |

| Table 17-2 Auto-Stop Generation                                        |     |

| Table 17-3 Non-data Transfer Commands and Requirements                 |     |

| Table 17-4 SDMMC IOMUX Settings                                        |     |

| Table 17-5 Recommended Usage of use_hold_reg                           |     |

| Table 17-6 Command Settings for No-Data Command                        | 646 |

| Table 17-7 Command Setting for Single-Block or Multiple-Block Read     |     |

| Table 17-8 Command Settings for Single-Block or Multiple-Block Write   |     |

| Table 17-9 Parameters for CMDARG Registers                             |     |

| Table 17-10 CMDARG Bit Values                                          |     |

| Table 22-1Hwc 3-color Transparency Mode                                |     |

| Table 22-2Hwc 2-color Transparency Mode                                |     |

| Table 22-3LCDC RGB/Y Data swap of WIN0, WIN1 and WIN2                  | 676 |

| Table 22-4LCDC CbCr Data swap of WIN0                                  |     |

| Table 22-5LCDC Scaling Start Point Offset Registers                    |     |

| Table 22-6 LCDC0 RGB interface signal timing constant                  |     |

| Table 22-7 LCDC1 RGB interface signal timing constant                  |     |

| Table 22-8 LCDC0 RGB interface signal timing constant                  |     |

| Table 22-9 LCDC1 RGB interface signal timing constant                  |     |

| Table 22-10 LCDC1 IOMUX                                                |     |

| Table 22-11 LCDC output nin definition                                 |     |

| Table 22-12 LCDC delta and swap setting for RGB delta LCD | 704  |

|-----------------------------------------------------------|------|

| Table 24-1CIF0 Timing                                     | 722  |

| Table 25-1 USB HOST 2.0 Interface Description             | 733  |

| Table 26-1 USB OTG 2.0 PHY power supply timing parameter  | 747  |

| Table 26-2 USB OTG 2.0 Interface Description              |      |

| Table 28-1 GPS IOMUX Settings                             | 892  |

| Table 29-1Meaning of the parameter in Fig. 29-11          | 908  |

| Table 29-2Meaning of the parameter in Fig. 29-12          |      |

| Table 31-1 SDMMC IOMUX Settings                           | 922  |

| Table 32-1 Management timing parameters                   | 936  |

| Table 32-2 RMii timing parameters                         | 937  |

| Table 32-3 RMII/MII Interface Description                 | 937  |

| Table 32-4 VMAC tx buffer descriptor                      | 941  |

| Table 32-5 VMAC- rx buffer descriptor for VMAC            | 942  |

| Table 32-6 VMAC-rx buffer descriptor for CPU              |      |

| Table 33-1 HS-ADC interface timing parameter              | 951  |

| Table 33-2 IOMUX configuration in ADC mode                | 952  |

| Table 33-3 IOMUX configuration in GPS mode                | 952  |

| Table 33-4 IOMUX configuration in TS mode                 | 952  |

| Table 35-1Meaning of the parameter in Fig.35-7            | 971  |

| Table 35-2Meaning of the parameter in Fig.35-8            | 972  |

| Table 35-3SPI interface description in master mode        | 972  |

| Table 35-4SPI interface description in slave mode         | 973  |

| Table 36-1 UART Interface Description                     | 991  |

| Table 36-2 UART baud rate configuration                   | 993  |

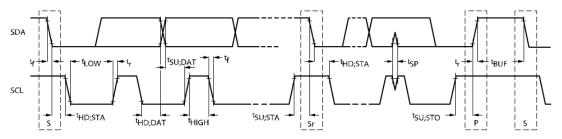

| Table 37-1 I2C timing parameters                          | 1006 |

| Table 37-2I2C Interface Description                       | 1006 |

| Table 40-1 PWM Interface Description                      | 1027 |

| Table 42-1 RK3168 eFuse timing parameters list            |      |

| Table 44-1 RK3168 test mode list                          | 1044 |

| Table 44-2 RK3168 jomux for misc signal in test mode      | 1045 |

# **Acronym Descriptions**

#### **Chapter 1 Introduction**

RK3168 is a low power, high performance processor for mobile phones, personal mobile internet device and other digital multimedia applications, and integrates dual-coreCortex-A9 with separately NEONand FPU coprocessor.

Many embedded powerful hardware engines provide optimized performance for high-end application. RK3168 supports almost full-format video decoder by 1080p@60fps, also support H.264 encoder by 1080p@30fps, high-quality JPEG encoder/decoder, special image preprocessor and postprocessor .

Embedded 3D GPU makes RK3168 completely compatible with OpenGL ES2.0 and 1.1, OpenVG 1.1. Special 2D hardware engine with MMU will maximize display performance and provide very smoothly operation.

RK3168 has high-performance external memory interface(DDR3/LPDDR2/LVDDR3) capable of sustaining demanding memory bandwidths, also provides a complete set of peripheral interface to support very flexible applications as follows:

- 2 banks, 8bits/16bits Nor Flash/SRAM interface

- 4 banks, 8bits/16bits async Nand Flash, LBA Nand Flash and 8bits sync ONFI Nand Flash, allup to 60bits hardware ECC

- Totally 2GB memory space for 2 ranks, 16bits/32bits DDR3-800, LPDDR2-800, LVDDR3-800

- Totally 3-channels SD/MMC interface to support MMC4.41, SD3.0, SDIO3.0 or eMMC

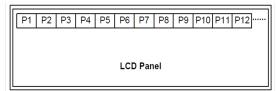

- 2-channels TFT LCD interface with 5-layers , 1920x1080 maximum display size

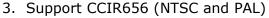

- Oe-channels, 8bits CCIR656 interface and 10bits/12bits raw data interface with image preprocessor

- Audio interface : one 2ch I2S/PCM interface and SPDIF tx interface

- 10M/100M RMII ethenet interface

- High-speed ADC interface and TS stream interface

- Lots of low-speed peripheral interface : 5I2C, 4UART, 2SPI,4PWM

This document will provide guideline on how to use RK3168 correctly and efficiently. The chapter 1 and chapter 2 will introduce the features, block diagram, signal descriptions and system usage of RK3168, the chapter 3 through chapter 45 will describe the full function of each module in detail.

#### 1.1 Features

#### 1.1.1 MicroProcessor

- Dual-core ARM Cortex-A9 MPCore processor, a high-performance, low-power and cached application processor

- Full implementation of the ARM architecture v7-A instruction set, ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerated media and signal processing computation

- Superscalar, variable length, out-of-order pipeline with dynamic branch prediction, 8-stage pipeline

- Include VFPv3 hardware to support single and double-precision add, subtract, divide, multiply and accumulate, and square root operations

- SCU ensures memory coherency between the two CPUs

- Integrated timer and watchdog timer per CPU

- Integrated 32KB L1 instruction cache , 32KB L1 data cache with 4-way set associative

- 256KB unified L2 Cache

- Trustzone technology support

- Full coresight debug solution

- Debug and trace visibility of whole systems

- ETM trace support

- Invasive and non-invasive debug

- One separate power domain for secondary core to support internal power switch and externally turn on/off based on different application scenario

- PD\_A9\_1: 2<sup>nd</sup> Cortex-A9 + Neon + FPU + L1 I/D Cache

- One isolated voltage domain to support DVFS

- Maximum frequency can be up to 1GHz@0.9V(Worst Case)

#### 1.1.2 Memory Organization

- Internal on-chip memory

- 10KB BootRom

- 16KB internal SRAM for security and non-security access, detailed size is programmable

- 128KB or 256KB internal SRAM shared with L2 Cache Memory

- External off-chip memory<sup>®</sup>

- DDR3-800, 16/32bits data widths, 2 ranks, totally 2GB(max) address space, maximum address space for one rank is also 2GB.

- LPDDR2-800, 32bits data width, 2 ranks, totally 2GB(max) address space, maximum address space for one rank is also 2GB.

- Async SRAM/Nor Flash, 8/16bits data width,2banks

- Async Nand Flash(include LBA Nand), 8/16bits data width,4 banks,60bits ECC

- Sync ONFI Nand Flash , 8bits data width, 8 banks, 60bits ECC

#### 1.1.3 Internal Memory

- Internal BootRom

- Size: 10KB

- Support system boot from the following device :

- ♦ 8bits/16bits Async Nand Flash

- 8bits ONFI Nand Flash

- ◆ SPI0 interface

- eMMC interface

- Support system code download by the following interface:

- ◆ USB OTG interface

- ◆ UARTO Interface

- Internal SRAM

- Size: 16KB

- Support security and non-security access

- Security or non-security space is software programmable

- Security space can be 0KB,4KB,8KB,12KB,16KB continuous size

- 128KB or 256KB internal SRAM shared with L2 Cache for Cortex-A9, size is configurable by software.

#### 1.1.4 External Memory or Storage device

- Dynamic Memory Interface (DDR3/LPDDR2)

- Compatible with JEDEC standard DDR3/LPDDR2 SDRAM

- Data rates up to 800Mbps(400MHz) for DDR3/LPDDR2

- Support up to 2 ranks (chip selects), totally 2GB(max) address space, maximum address space for one rank is also 2GB, which is software-configurable.

- 16bits/32bits data width is software programmable

- 5 host ports with 64bits AXI bus interface for system access, AXI bus clock is asynchronous with DDR clock

- Programmable timing parameters to support DDR3/LPDDR2 SDRAM from various vendor

- Advanced command reordering and scheduling to maximize bus utilization

- Low power modes, such as power-down and self-refresh for DDR3/LPDDR2 SDRAM; clock stop and deep power-down forLPDDR2 SDRAM

- Compensation for board delays and variable latencies through programmable pipelines

- Embedded dynamic drift detection in the PHY to get dynamic drift compensation with the controller

- Programmable output and ODT impedance with dynamic PVT compensation

- Support one low-power work mode: power down DDR PHY and most of DDR IO except two cs and two cke output signals, make SDRAM still in self-refresh state to prevent data missing.

- Static Memory Interface (ASRAM/Nor Flash)

- Compatible with standard async SRAM or Nor Flash

- Support up to 2 banks (chip selects)

- For bank0, 8bits/16bits data width is software programmable; For bank1, 16bits data width is fixed

- Support separately data and address bus, also support shared data and address bus to save IO numbers

#### Nand Flash Interface

- Support 8bits/16bits async nand flash, up to 4 banks

- Support 8bits sync DDR nand flash, up to 4 banks

- Support LBA nand flash in async or sync mode

- Up to 60bits hardware ECC

- For DDR nand flash, support DLL bypass and 1/4 or 1/8 clock adjust, maximum clock rate is 75MHz

- For async nand flash, support configurable interface timing , maximum data rate is 16bit/cycle

- Embedded special DMA interface to do data transfer

- Also support data transfer together with general DMAC1 in SoC system

#### eMMC Interface

- Compatible with standard iNAND interface

- Support MMC4.41 protocol

- Provide eMMC boot sequence to receive boot data from external eMMC device

- Support combined single FIFO(32x32bits) for both transmit and receive operations

- Support FIFO over-run and under-run prevention by stopping card clock automatically

- Support CRC generation and error detection

- Embedded clock frequency division control to provide programmable baud rate