# Chapter 10 DMA Controller for Bus System (DMAC\_BUS)

## 10.1 Overview

This device supports 2 Direct Memory Access (DMA) tops, one for cpu system (DMAC\_BUS), and the other one for Peripheral system (PERI\_DMAC).Both of these two dma support transfers between memory and memory, peripheral and memory.

DMAC\_BUS supports TrustZone technology and is under secure state after reset. The secure state can be changed by configuring TZPC module.

DMAC\_BUS is mainly used for data transfer of the following slaves: I2S0/I2S1/SPDIF/UART0/Embedded SRAM and transfer data from/to external DDR SDRAM.

Following table shows the DMAC\_BUS peripheral request mapping scheme.

Table 10-1 DMAC\_BUS Request Mapping Table

| Req number | Source      | Polarity   |

|------------|-------------|------------|

| 0          | I2S tx      | High level |

| 1          | I2S rx      | High level |

| 2          | SPDIF       | High level |

| 3          | SPDIF (8ch) | High level |

| 4          | UART DBG tx | High level |

| 5          | UART DBG rx | High level |

DMAC\_BUS supports the following features:

- Supports Trustzone technology

- Supports 6 peripheral request

- Up to 64bits data size

- 5 channel at the same time

- Up to burst 16

- 10 interrupt output and 1 abort output

- Supports 32 MFIFO depth

# 10.2 Block Diagram

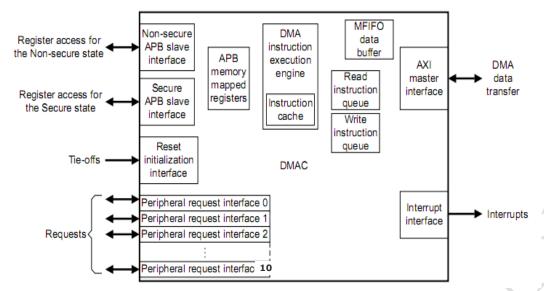

Figure 10-1 shows the block diagram of DMAC\_BUS

Fig. 10-1 Block diagram of DMAC\_BUS

As the DMAC\_BUS supports Trustzone technology, so dual APB interfaces enable the operation of the DMAC\_BUS to be partitioned into the secure state and Non-secure state. You can use the APB interfaces to access status registers and also directly execute instructions in the DMAC\_BUS. The default interface after reset is secure apb interface.

# 10.3 Function Description

#### 10.3.1 Introduction

The DMAC contains an instruction processing block that enables it to process program code that controls a DMA transfer. The program code is stored in a region of system memory that the DMAC accesses using its AXI interface. The DMAC stores instructions temporarily in a cache.

DMAC\_BUS supports 6 channels, each channel capable of supporting a single concurrent thread of DMA operation. In addition, a single DMA manager thread exists, and you can use it to initialize the DMA channel threads. The DMAC executes up to one instruction for each AXI clock cycle. To ensure that it regularly executes each active thread, it alternates by processing the DMA manager thread and then a DMA channel thread. It uses a round-robin process when selecting the next active DMA channel thread to execute.

The DMAC uses variable-length instructions that consist of one to six bytes. It provides a separate Program Counter (PC) register for each DMA channel. When a thread requests an instruction from an address, the cache performs a look-up. If a cache hit occurs, then the cache immediately provides the data. Otherwise, the thread is stalled while the DMAC uses the AXI interface to perform a cache line fill. If an instruction is greater than 4 bytes, or spans the end of a cache line, the DMAC performs multiple cache accesses to fetch the instruction.

When a cache line fill is in progress, the DMAC enables other threads to access the cache, but if another cache miss occurs, this stalls the pipeline until the first line fill is complete.

When a DMA channel thread executes a load or store instruction, the DMAC adds the instruction to the relevant read or write queue. The DMAC uses these queues as an instruction storage buffer prior to it issuing the instructions on the AXI bus. The DMAC also contains a Multi First-In-First-Out (MFIFO) data buffer that it uses to store data that it reads, or writes, during a DMA transfer.

# 10.3.2 Operating states

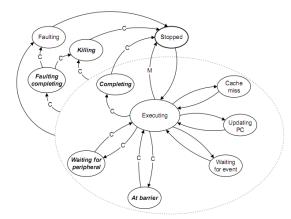

Figure shows the operating states for the DMA manager thread and DMA channel threads.

Fig. 10-2 DMAC\_BUS operation states

#### Note:

arcs with no letter designator indicate state transitions for the DMA manager and DMA channel threads, otherwise use is restricted as follows:

C DMA channel threads only.

M DMA manager thread only.

After the DMAC exits from reset, it sets all DMA channel threads to the stopped state, and the status of boot\_from\_pc(tie-off interface of dmac) controls the DMA manager thread state:

boot\_from\_pc is LOW :DMA manager thread moves to the Stopped state. boot\_from\_pc is HIGH :DMA manager thread moves to the Executing state.

# 10.4 Register Description

# 10.4.1 Register summary

| Name                   | Offset | Size | Reset<br>Value | Description                           |  |  |  |

|------------------------|--------|------|----------------|---------------------------------------|--|--|--|

| DMAC_BUS_DSR           | 0x0000 | W    | 0x0            | DMA Status Register.                  |  |  |  |

| DMAC_BUS_DPC           | 0x0004 | W    | 0x0            | DMA Program Counter<br>Register.      |  |  |  |

| -                      |        | - '  | -              | reserved                              |  |  |  |

| DMAC_BUS_INTE N        | 0x0020 | W    | 0x0            | Interrupt Enable Register             |  |  |  |

| DMAC_BUS_EVE<br>NT_RIS | 0x0024 | W    | 0x0            | Event Status Register.                |  |  |  |

| DMAC_BUS_INT<br>MIS    | 0x0028 | W    | 0x0            | Interrupt Status Register             |  |  |  |

| DMAC_BUS_INTC<br>LR    | 0x002C | W    | 0x0            | Interrupt Clear Register              |  |  |  |

| DMAC_BUS_FSR<br>D      | 0x0030 | W    | 0x0            | Fault Status DMA Manager<br>Register. |  |  |  |

| DMAC_BUS_FSR<br>C      | 0x0034 | W    | 0x0            | Fault Status DMA Channel Register.    |  |  |  |

| DMAC_BUS_FTR<br>D      | 0x0038 | W    | 0x0            | Fault Type DMA Manager<br>Register.   |  |  |  |

| -                      | -      | -    | -              | reserved                              |  |  |  |

| DMAC_BUS_FTR0          | 0x0040 | W    | 0x0            | Fault type for DMA Channel 0          |  |  |  |

| DMAC BUS_FIR2         0x0048         W         0x0         Fault type for DMA Channel 2           DMAC BUS_FIR3         0x0048         W         0x0         Fault type for DMA Channel 2           DMAC BUS_FIR3         0x0050         W         0x0         Fault type for DMA Channel 3           DMAC BUS_FIR5         0x0054         W         0x0         Fault type for DMA Channel 4           DMAC BUS_FIR5         0x0054         W         0x0         Fault type for DMA Channel 5           -         -         -         -         reserved           DMAC_BUS_CSR         0x0100         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0110         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0128         W         0x0         Channel Status for DMA Channel 4           DMAC_BUS_CCSR         0x0128         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CCPC         0x0104         W         0x0         Channel Status for DMA Channel 9           DMAC_BUS_CCPC         0x010c         W         0x0         Channel PC for DMA Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |          |             |      | I = 1,                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|-------------|------|-------------------------------|

| DMAC_BUS_FTR3   0x004C   W   0x0   Fault type for DMA Channel 3   DMAC_BUS_FTR5   0x0054   W   0x0   Fault type for DMA Channel 4   Fault type for DMA Channel 5   Fault type for DMA Channel 5   Fault type for DMA Channel 6   Fault type for DMA Channel 7   Fault type for DMA Channel 7   Fault type for DMA Channel 8   Fault type for DMA Channel 8   Fault type for DMA Channel 9   Fault type for DMA Ch   | DMAC_BUS_FTR1 | 0x0044   | W           | 0x0  | Fault type for DMA Channel 1  |

| DMAC_BUS_FTR4         0x0050         W         0x0         Fault type for DMA Channel 4           DMAC_BUS_FTR5         0x0054         W         0x0         Fault type for DMA Channel 5           -         -         -         -         -         -           DMAC_BUS_CSR         0x0100         W         0x0         Channel Status for DMA Channel 1           DMAC_BUS_CSR         0x0110         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CSR         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CCR         0x0128         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CCPC         0x0104         W         0x0         Channel Status for DMA Channel 7           DMAC_BUS_CCPC         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CCPC         0x0110         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC         0x0114         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC         0x0124         W         0x0         Channel PC for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |          |             |      |                               |

| DMAC_BUS_FTR5         0x0054         W         0x0         Fault type for DMA Channel 5           DMAC_BUS_CSR         0x0100         W         0x0         Channel 7         Channel 7         DMAC_BUS_CSR         DMAC_BUS_CSR         0x0100         W         0x0         Channel 7         Channel 7         Channel 7         Channel 7         DMAC_BUS_CSR         0x0110         W         0x0         Channel 2         Channel 3         Channel 2         Channel 3         Channel 2         Channel 3         Channel 3         Channel 3         Channel 3         Channel 2         Channel 3         Channel 2         Channel 2         Channel 3         Channel 2         Channel 2 <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |          |             |      |                               |

| DMAC_BUS_CSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DMAC_BUS_FTR4 | 0x0050   |             | 0x0  |                               |

| DMAC_BUS_CSR<br>0         0x0100         W         0x0         Channel Channel Channel Channel Channel Status         for DMA Channel 1           DMAC_BUS_CSR<br>1         0x0108         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CSR<br>2         0x0110         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CSR<br>4         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR<br>4         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR<br>4         0x0128         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CPC<br>0         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC<br>1         0x0104         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC<br>2         0x0114         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC<br>2         0x0112         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_CPC<br>4         0x0122         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR<br>0         0x0400         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR<br>2 <td>DMAC_BUS_FTR5</td> <td>0x0054</td> <td>W</td> <td>0x0</td> <td>Fault type for DMA Channel 5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DMAC_BUS_FTR5 | 0x0054   | W           | 0x0  | Fault type for DMA Channel 5  |

| 0         0X0100         W         0X0         Channel 0         Channel 1         Channel 1         DMAC_BUS_CSR         0x0110         W         0x0         Channel Status for DMA Channel 1           DMAC_BUS_CSR 2         0x0110         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 3         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 4         0x0128         W         0x0         Channel Status for DMA Channel 4           DMAC_BUS_CPC 0x0104         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC 0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0x0114         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC 0x0124         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC 0x0124         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR 0x0400         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR 0x0440         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR 0x0440         W         0x0 </td <td>-</td> <td>-</td> <td>ı</td> <td>-</td> <td>reserved</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -             | -        | ı           | -    | reserved                      |

| 0         0X0100         W         0X0         Channel 0         Channel 1         Channel 1         DMAC_BUS_CSR         0x0110         W         0x0         Channel Status for DMA Channel 1           DMAC_BUS_CSR 2         0x0110         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 3         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 4         0x0128         W         0x0         Channel Status for DMA Channel 4           DMAC_BUS_CPC 0x0104         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC 0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0x0114         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC 0x0124         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC 0x0124         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR 0x0400         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR 0x0440         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR 0x0440         W         0x0 </td <td>DMAC BUS CSR</td> <td>0.0100</td> <td>147</td> <td>0.0</td> <td>Channel Status for DMA</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DMAC BUS CSR  | 0.0100   | 147         | 0.0  | Channel Status for DMA        |

| DMAC_BUS_CSR 1         0x0108         W         0x0         Channel Status for DMA Channel 1           DMAC_BUS_CSR 2         0x0110         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CSR 3         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 4         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR 5         0x0128         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC 0         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 0         0x0114         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC 0         0x011c         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC 0         0x0124         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR 0         0x0400         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR 0x0440         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR 0x0440         W         0x0         Source Addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 0X0100   | VV          | UXU  |                               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DMAC BUS CSR  |          |             |      |                               |

| DMAC_BUS_CSR         0x0110         W         0x0         Channel Status for DMA Channel 2           DMAC_BUS_CSR         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0120         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0128         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC         0x010c         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC         0x011d         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC         0x011c         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC         0x012d         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR         0x0400         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR         0x0440         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR         0x0440         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR         0x0440         W         0x0         Sourc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 0x0108   | W           | 0x0  |                               |

| DMAC_BUS_CPC   Ox0114   W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |          |             |      |                               |

| DMAC_BUS_CSR         0x0118         W         0x0         Channel Status for DMA Channel 3           DMAC_BUS_CSR         0x0120         W         0x0         Channel Status for DMA Channel 4           DMAC_BUS_CSR         0x0128         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC         0x010c         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC         0x0114         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC         0x011c         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_CPC         0x012d         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR         0x0400         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR         0x0400         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_SAR         0x0420         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR         0x0440         W         0x0         Source Address for DMA Channel 5           DMAC_BUS_SAR         0x0440         W         0x0         Sourc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 0x0110   | W           | 0x0  |                               |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |          |             |      |                               |

| DMAC_BUS_CSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 0x0118   | W           | 0x0  |                               |

| 4         0x0120         W         0x0         Channel 4           DMAC_BUS_CSR 5         0x0128         W         0x0         Channel Status for DMA Channel 5           DMAC_BUS_CPC 0         0x0104         W         0x0         Channel PC for DMA Channel 0           DMAC_BUS_CPC 1         0x010c         W         0x0         Channel PC for DMA Channel 1           DMAC_BUS_CPC 2         0x0114         W         0x0         Channel PC for DMA Channel 2           DMAC_BUS_CPC 3         0x011c         W         0x0         Channel PC for DMA Channel 3           DMAC_BUS_CPC 4         0x012d         W         0x0         Channel PC for DMA Channel 4           DMAC_BUS_CPC 5         0x012c         W         0x0         Channel PC for DMA Channel 4           DMAC_BUS_SAR 0x0400         0x0400         W         0x0         Source Address for DMA Channel 5           DMAC_BUS_SAR 1         0x0420         W         0x0         Source Address for DMA Channel 1           DMAC_BUS_SAR 2         0x0440         W         0x0         Source Address for DMA Channel 2           DMAC_BUS_SAR 3         0x0460         W         0x0         Source Address for DMA Channel 2           DMAC_BUS_DAR 3         0x0440         W         0x0         So                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |          |             |      |                               |

| DMAC_BUS_CPC DMAC_BUS_SAR DMAC_BUS_DAR DMAC_ | DMAC_BUS_CSR  | 0x0120   | \٨/         | 0×0  |                               |

| DMAC_BUS_CPC DMAC_BUS_SAR DMAC_BUS_DAR DMAC_ | 4             | 0.0120   | V V         | 0.00 | Channel 4                     |

| DMAC_BUS_CPC  0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DMAC_BUS_CSR  | 0v0120   | ۱۸/         | 0.40 | Channel Status for DMA        |

| DMAC_BUS_CPC DMAC_BUS_SAR DMAC_BUS_DAR DMAC_BUS_CCR DMACABUS DMA | 5             | UXU128   | VV          | UXU  | Channel 5                     |

| DMAC_BUS_CPC DMAC_BUS_SAR DMAC_BUS_DAR DMAC_BUS_CCR DMACABUS DMA | DMAC BUS CPC  | 0.0101   |             | 0 0  |                               |

| DMAC_BUS_CPC 1 DMAC_BUS_CPC 2 DMAC_BUS_CPC 2 DMAC_BUS_CPC 3 DMAC_BUS_CPC 3 DMAC_BUS_CPC 3 DMAC_BUS_CPC 3 DMAC_BUS_CPC 3 DMAC_BUS_CPC 4 DMAC_BUS_CPC 5 DMAC_BUS_CPC 5 DMAC_BUS_SAR 0 0x0420 DMAC_BUS_SAR 1 DMAC_BUS_SAR 3 DMAC_BUS_SAR 3 DMAC_BUS_SAR 4 DMAC_BUS_SAR 4 DMAC_BUS_SAR 3 DMAC_BUS_SAR 4 DMAC_BUS_SAR 5 DMAC_BUS_SAR 0x0440 W 0x0 DMAC_BUS_SAR 3 DMAC_BUS_SAR 4 DMAC_BUS_SAR 4 DMAC_BUS_SAR 5 DMAC_BUS_SAR 4 DMAC_BUS_SAR 5 DMAC_BUS_SAR 5 DMAC_BUS_SAR 6 DMAC_BUS_SAR 6 DMAC_BUS_SAR 7 DMAC_BUS_DAR 7 DMAC_BUS_CCR 7 DMAC 7 DM |               | 0x0104   | W           | 0x0  | Channel PC for DMA Channel 0  |

| DMAC_BUS_CPC DMAC_BUS_CPC Nov0114 W 0x0 Channel PC for DMA Channel 2 DMAC_BUS_CPC CALL DMAC_BUS_CPC DMAC_BUS_CPC CALL DMAC_BUS_CPC CALL DMAC_BUS_CPC CALL DMAC_BUS_CPC CALL DMAC_BUS_CPC CALL DMAC_BUS_CPC CALL DMAC_BUS_SAR CALL CALL DMAC_BUS_SAR CALL CALL DMAC_BUS_SAR CALL CALL CALL CALL CALL CALL CALL CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -             |          |             |      | A (2) Y                       |

| DMAC_BUS_CPC 2 DMAC_BUS_CPC 3 DMAC_BUS_CPC 3 DMAC_BUS_CPC 4 0x011c W 0x0 Channel PC for DMA Channel 2 Channel PC for DMA Channel 3 DMAC_BUS_CPC 4 DMAC_BUS_CPC 5 0x012c W 0x0 Channel PC for DMA Channel 4 DMAC_BUS_SAR 0x0400 W 0x0 Channel PC for DMA Channel 5 DMAC_BUS_SAR 0x0400 W 0x0 Channel PC for DMA Channel 5 Source Address for DMA Channel 0 Source Address for DMA Channel 1 Channel 1 DMAC_BUS_SAR 1 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 2 DMAC_BUS_SAR 3 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 3 Source Address for DMA Channel 3 Source Address for DMA Channel 3 DMAC_BUS_SAR 0x0460 W 0x0 Source Address for DMA Channel 4 DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 5 DMAC_BUS_DAR 0x0440 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 4 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 6 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 6 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 6 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 6 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 6 DMAC_BUS_DAR 0x0404 W 0x0 DMAC_BUS_DA | I . — —       | 0x010c   | W           | 0x0  | Channel PC for DMA Channel 1  |

| DMAC_BUS_CPC DMAC_BUS_CPC DMAC_BUS_CPC DMAC_BUS_CPC DMAC_BUS_CPC DMAC_BUS_CPC S DMAC_BUS_CPC S DMAC_BUS_SAR Ox0400 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0420 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0460 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0480 DMAC_BUS_SAR S DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0460 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_SAR S DMAC_BUS_SAR Ox0440 DMAC_BUS_CAR Ox0440 DMAC_BUS_CAR Ox0440 DMAC_BUS_CAR Ox0440 DMAC_BUS_DAR Ox0440 DMAC_BUS_DAR Ox0444 D |               |          |             |      | •                             |

| DMAC_BUS_CPC 3 DMAC_BUS_CPC 4 0x0124 W 0x0 Channel PC for DMA Channel 3 DMAC_BUS_CPC 5 0x012c W 0x0 Channel PC for DMA Channel 4 DMAC_BUS_SAR 0 0x0400 W 0x0 DMAC_BUS_SAR 0 0x0420 W 0x0 Source Address for DMA Channel 0 Source Address for DMA Channel 1 Source Address for DMA Channel 2 DMAC_BUS_SAR 0x0440 W 0x0 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 2 Source Address for DMA Channel 3 Source Address for DMA Channel 4 Source Address for DMA Channel 4 Source Address for DMA Channel 5 DMAC_BUS_SAR 0x0480 W 0x0 DMAC_BUS_SAR 0x0480 W 0x0 DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 0 DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x04 |               | 0x0114   | W           | 0x0  | Channel PC for DMA Channel 2  |

| DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 3  DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 1  DMAC_BUS_SAR Ox0420 W Ox0 Source Address for DMA Channel 1  DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 1  DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 1  DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 2  DMAC_BUS_SAR Ox0460 W Ox0 Source Address for DMA Channel 3  DMAC_BUS_SAR Ox0480 W Ox0 Source Address for DMA Channel 3  DMAC_BUS_SAR Ox0440 W Ox0 Source Address for DMA Channel 3  DMAC_BUS_SAR Ox0480 W Ox0 Source Address for DMA Channel 4  DMAC_BUS_SAR Ox0440 W Ox0 Dest Address for DMA Channel 5  DMAC_BUS_DAR Ox0404 W Ox0 Dest Address for DMAChannel 1  DMAC_BUS_DAR Ox0424 W Ox0 Dest Address for DMAChannel 1  DMAC_BUS_DAR Ox0444 W Ox0 Dest Address for DMAChannel 2  DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel 3  DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel 3  DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel 3  DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel 3  DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel 3  DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel 4  DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel 5  DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel 5  DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel 5  DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel 5  DMAC_BUS_DAR Ox0488 W Ox0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |          |             |      | X                             |

| DMAC_BUS_CPC  DMAC_BUS_CPC  DMAC_BUS_SAR  O  DMAC_BUS_DAR  O  DMAC_BUS_CCR  O  DMAC_BUS_CCR  O  DMAC_BUS_CCR  O  DMAC_BUS_CCR  O  DMAC_BUS_CCR  O  DMAC  Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                     |               | 0x011c   | W           | 0x0  | Channel PC for DMA Channel 3  |

| DMAC_BUS_SAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |          |             |      |                               |

| DMAC_BUS_CPC         0x012c         W         0x0         Channel PC for DMA Channel 5           DMAC_BUS_SAR         0x0400         W         0x0         Source Address for DMA Channel 0           DMAC_BUS_SAR         0x0420         W         0x0         Source Address for DMA Channel 1           DMAC_BUS_SAR         0x0440         W         0x0         Source Address for DMA Channel 2           DMAC_BUS_SAR         0x0460         W         0x0         Source Address for DMA Channel 3           DMAC_BUS_SAR         0x0480         W         0x0         Source Address for DMA Channel 3           DMAC_BUS_SAR         0x04a0         W         0x0         Source Address for DMA Channel 4           DMAC_BUS_DAR         0x04a0         W         0x0         Dest Address for DMA Channel 5           DMAC_BUS_DAR         0x0404         W         0x0         Dest Address for DMA Channel 1           DMAC_BUS_DAR         0x0424         W         0x0         Dest Address for DMA Channel 2           DMAC_BUS_DAR         0x0464         W         0x0         Dest Address for DMA Channel 3           DMAC_BUS_DAR         0x0484         W         0x0         Dest Address for DMA Channel 4           DMAC_BUS_DAR         0x0484         W         0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DMAC_BUS_CPC  | 0x0124   | \٨/         | 0×0  | Channel PC for DMA Channel 4  |

| DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 1 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 1 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 2 DMAC_BUS_SAR 0x0460 W 0x0 Source Address for DMA Channel 2 DMAC_BUS_SAR 0x0460 W 0x0 Source Address for DMA Channel 3 DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 3 DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 4 DMAC_BUS_SAR 0x0440 W 0x0 Source Address for DMA Channel 5 DMAC_BUS_DAR 0x0440 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1 DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3 DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 4 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5 DMAC_BUS_DAR 0x0488 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4             | 0.0121   | • • •       | ONO  | Chamier Color Drive Chamier 1 |

| DMAC_BUS_SAR 0x0400 W 0x0 Source Address for DMA Channel 0  DMAC_BUS_SAR 1 0x0420 W 0x0 Source Address for DMA Channel 1  DMAC_BUS_SAR 2 0x0440 W 0x0 Source Address for DMA Channel 2  DMAC_BUS_SAR 3 0x0460 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 5  DMAC_BUS_DAR 0x0440 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_CCR 0x0408 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DMAC_BUS_CPC  | 0v012c   | ۱۸/         | 0×0  | Channel BC for DMA Channel 5  |

| DMAC_BUS_DAR Ox0420 W Ox0 Channel 0  DMAC_BUS_SAR 1  DMAC_BUS_SAR 2  DMAC_BUS_SAR 3  DMAC_BUS_SAR 4  DMAC_BUS_DAR 5  DMAC_BUS_DAR 1  DMAC_BUS_DAR 1  DMAC_BUS_DAR 2  DMAC_BUS_DAR 3  DMAC_BUS_DAR 3  DMAC_BUS_DAR 3  DMAC_BUS_DAR 4  DMAC_BUS_DAR 4  DMAC_BUS_DAR 5  DMAC_BUS_DAR 5  DMAC_BUS_DAR 6  DMAC_BUS_DAR 7  DMAC_BUS_CCR 7  DMAC_BUS_ | 5             | 0.0120   | VV          | 0.00 | Chairle FC 101 DMA Chairle 3  |

| DMAC_BUS_SAR 1 0x0420 W 0x0 Source Address for DMA Channel 1  DMAC_BUS_SAR 2 0x0440 W 0x0 Source Address for DMA Channel 2  DMAC_BUS_SAR 3 0x0460 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 4 0x0480 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 0x04a0 W 0x0 Source Address for DMA Channel 5  DMAC_BUS_DAR 0x04a0 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_CCR 0x0488 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DMAC_BUS_SAR  | 0,0400   | 147         | 00   | Source Address for DMA        |

| 10x0420W0x0Channel 1DMAC_BUS_SAR<br>20x0440W0x0Source Address for DMA<br>Channel 2DMAC_BUS_SAR<br>30x0460W0x0Source Address for DMA<br>Channel 3DMAC_BUS_SAR<br>40x0480W0x0Source Address for DMA<br>Channel 4DMAC_BUS_SAR<br>50x04a0W0x0Source Address for DMA<br>Channel 5DMAC_BUS_DAR<br>00x0404W0x0Dest Address for DMAChannel<br>0DMAC_BUS_DAR<br>20x0424W0x0Dest Address for DMAChannel<br>1DMAC_BUS_DAR<br>30x0444W0x0Dest Address for DMAChannel<br>2DMAC_BUS_DAR<br>40x0464W0x0Dest Address for DMAChannel<br>3DMAC_BUS_DAR<br>40x0484W0x0Dest Address for DMAChannel<br>4DMAC_BUS_DAR<br>50x04a4W0x0Dest Address for DMAChannel<br>4DMAC_BUS_CCR0x04a4W0x0Dest Address for DMAChannel<br>5DMAC_BUS_CCR0x04a8W0x0Dest Address for DMAChannel<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0             | UXU4UU   | VV          | UXU  | Channel 0                     |

| 10x0420W0x0Channel 1DMAC_BUS_SAR<br>20x0440W0x0Source Address for DMA<br>Channel 2DMAC_BUS_SAR<br>30x0460W0x0Source Address for DMA<br>Channel 3DMAC_BUS_SAR<br>40x0480W0x0Source Address for DMA<br>Channel 4DMAC_BUS_SAR<br>50x04a0W0x0Source Address for DMA<br>Channel 5DMAC_BUS_DAR<br>00x0404W0x0Dest Address for DMAChannel<br>0DMAC_BUS_DAR<br>20x0424W0x0Dest Address for DMAChannel<br>1DMAC_BUS_DAR<br>30x0444W0x0Dest Address for DMAChannel<br>2DMAC_BUS_DAR<br>40x0464W0x0Dest Address for DMAChannel<br>3DMAC_BUS_DAR<br>40x0484W0x0Dest Address for DMAChannel<br>4DMAC_BUS_DAR<br>50x04a4W0x0Dest Address for DMAChannel<br>4DMAC_BUS_CCR0x04a4W0x0Dest Address for DMAChannel<br>5DMAC_BUS_CCR0x04a8W0x0Dest Address for DMAChannel<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DMAC BUS SAR  | 0.0400   |             |      | Source Address for DMA        |

| DMAC_BUS_SAR 2 0x0440 W 0x0 Source Address for DMA Channel 2  DMAC_BUS_SAR 3 0x0460 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 0x0480 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 0x04a0 W 0x0 Source Address for DMA Channel 5  DMAC_BUS_DAR 0x0440 W 0x0 Dest Address for DMAChannel 0  DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_CCR 0x0408 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | 0x0420   | W           | 0x0  |                               |

| DMAC_BUS_SAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |          |             |      |                               |

| DMAC_BUS_SAR 3 0x0460 W 0x0 Source Address for DMA Channel 3  DMAC_BUS_SAR 4 0x0480 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 5 0x04a0 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 0x04a0 W 0x0 Dest Address for DMA Channel 5  DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_CCR 0x0408 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 0x0440   | W           | 0x0  |                               |

| DMAC_BUS_SAR Ox0480 W Ox0 Channel 3  Source Address for DMA Channel 4  DMAC_BUS_SAR Ox04a0 W Ox0 Source Address for DMA Channel 4  Source Address for DMA Channel 5  DMAC_BUS_DAR Ox0404 W Ox0 Dest Address for DMAChannel Ox0424 DMAC_BUS_DAR Ox0444 W Ox0 Dest Address for DMAChannel Ox0424 DMAC_BUS_DAR Ox0444 W Ox0 Dest Address for DMAChannel Ox0464 DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel Ox0464 DMAC_BUS_DAR Ox0464 W Ox0 Dest Address for DMAChannel Ox0464 DMAC_BUS_DAR Ox0484 W Ox0 Dest Address for DMAChannel Ox0484 DMAC_BUS_DAR Ox0484 DMAC_BUS_DAR Ox0484 DMAC_BUS_CCR Ox0408 DMAC_BUS_CCR Ox0408 Channel 3  Channel Control for DMA Channel Channel Control for DMA Channel Ox0408 Channel 3  Channel Control for DMA Channel Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               | A 1      |             |      |                               |

| DMAC_BUS_SAR 4 0x0480 W 0x0 Source Address for DMA Channel 4  DMAC_BUS_SAR 5 0x04a0 W 0x0 Source Address for DMA Channel 5  DMAC_BUS_DAR 0x0404 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0424 W 0x0 Dest Address for DMAChannel 1  DMAC_BUS_DAR 0x0444 W 0x0 Dest Address for DMAChannel 2  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0464 W 0x0 Dest Address for DMAChannel 3  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 4  DMAC_BUS_DAR 0x0484 W 0x0 Dest Address for DMAChannel 5  DMAC_BUS_CCR 0x0408 W 0x0 Channel Control for DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | 0x0460   | W           | 0x0  |                               |