# Chapter 26 USB OTG 2.0

# 26.1 Overview

USB OTG 2.0 is a Dual-Role Device controller, which supports both device and host functions and is fully compliant with OTG Supplement to USB2.0 specification, and support high-speed (480Mbps), full-speed (12Mbps), low-speed (1.5Mbps) transfer.

USB OTG 2.0 is optimized for portable electronic devices, point-to-point applications (no hub, direct connection to device) and multi-point applications to devices. USB OTG 2.0 interface supports both device and host functions and is fully compliant with OTG Supplement to USB2.0 specification, and support high-speed (480Mbps), full-speed (12Mbps), low-speed (1.5Mbps) transfer. It is optimized for portable electronic device, point-to-point applications (no hub, direct connection to device) and multi-point applications to devices.

### 26.1.1 Features

- Compliant with the OTG Supplement to the USB2.0 Specification

- Operates in High-Speed and Full-Speed mode

- Support 9 channels in host mode

- 9 Device mode endpoints in addition to control endpoint 0, 4 in, 3 out and 2 IN/OUT

- ♦ Built-in one 1024x35 bits FIFO

- Internal DMA with scatter/gather function

- Supports packet-based, dynamic FIFO memory allocation for endpoints for flexible, efficient use of RAM

- Support dynamic FIFO sizing

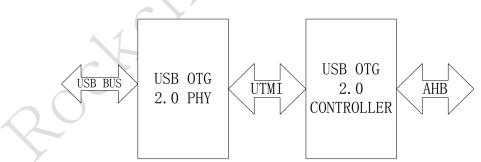

Fig. 26-1 USB OTG 2.0 Architecture

Fig.26-1 shows the architecture of USB OTG 2.0. It is broken up into two separate units: USB OTG 2.0 controller and USB OTG 2.0 PHY. The two units are interconnected with UTMI interface.

### 26.2.1 USB OTG 2.0 Controller Function

The USB OTG 2.0 Controller controls SIE (Serial Interface Engine) logic, the endpoint logic, the channel logic and the internal DMA logic.

The SIE logic contains the USB PID and address recognition logic, and other sequencing and state machine logic to handle USB packets and transactions.

1036

Generally the SIE Logic is required for any USB implementation while the number and types of endpoints will vary as function of application and performance requirements.

The endpoint logic contains the endpoint specific logic: endpoint number recognition, FIFOs and FIFO control, etc.

The channel Logic contains the channel tasks schedule, FIFOs and FIFO control, etc.

The internal DMA logic controls data transaction between system memory and USB FIFOs.

### 26.2.2 USB OTG 2.0 PHY Function

The USB OTG 2.0 PHY handles the low level USB protocol and signaling. This includes features such as; data serialization and deserialization, bit stuffing and clock recovery and synchronization. The primary focus of this block is to shift the clock domain of the data from the USB 2.0 rate to the frequency of UTMI clock which is 30MHz.

### 26.2.3 UTMI Interface

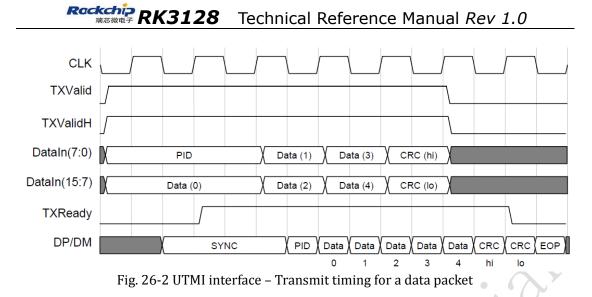

• Transmit

Transmit must be asserted to enable any transmissions.

The USB OTG2.0 CONTROLLER asserts TXValid to begin a transmission and negates TXValid to end a transmission. After the USB OTG2.0 CONTROLLER asserts TXValid it can assume that the transmission has started when it detects TXReady asserted.

The USB OTG2.0 CONTROLLER assumes that the USB OTG2.0 PHY has consumed a data byte if TXReady and TXValid are asserted.

The USB OTG2.0 CONTROLLER must have valid packet information (PID) asserted on the Data In bus coincident with the assertion of TXValid. Depending on the USB OTG2.0 PHY implementation, TXReady may be asserted by the Transmit State Machine as soon as one CLK after the assertion of TXValid. TXValid and TXReady are sampled on the rising edge of CLK.

The Transmit State Machine does NOT automatically generate Packet ID's (PIDs) or CRC. When transmitting, the USB OTG2.0 CONTROLLER is always expected to present a PID as the first byte of the data stream and if appropriate, CRC as the last bytes of the data stream.

The USB OTG2.0 CONTROLLER must use LineState to verify a Bus Idle condition before asserting TXValid in the TX Wait state.

The state of TXReady in the TX Wait and Send SYNC states is undefined. An MTU implementation may prepare for the next transmission immediately after the Send EOP state and assert TXReady in the TX Wait state. An MTU implementation may also assert TXReady in the Send SYNC state. The first assertion of TXReady is Macrocell implementation dependent. The USB OTG2.0 CONTROLLER must prepare DataIn for the first byte to be transmitted before asserting TXValid.

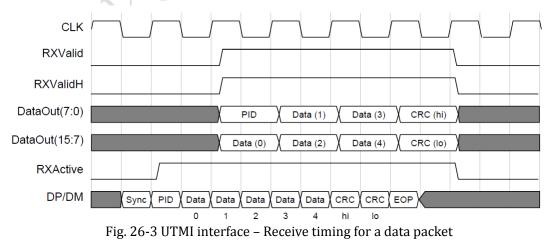

Receive

RXActive and RXValid are sampled on the rising edge of CLK.

In the RX Wait state the receiver is always looking for SYNC.

The USB OTG 2.0 PHY asserts RXActive when SYNC is detected (Strip SYNC state).

The USB OTG 2.0 PHY negates RXActive when an EOP is detected (Strip EOP state).

When RxActive is asserted, RXValid will be asserted if the RX Holding Register is full.

RXValid will be negated if the RX Holding Register was not loaded during the previous byte time.

This will occur if 8 stuffed bits have been accumulated.

The USB OTG2.0 Controller must be ready to consume a data byte if RXActive and RXValid are asserted (RX Data state).

In FS mode, if a bit stuff error is detected then the Receive State Machine will negate RXActive and RXValid, and return to the RX Wait state.

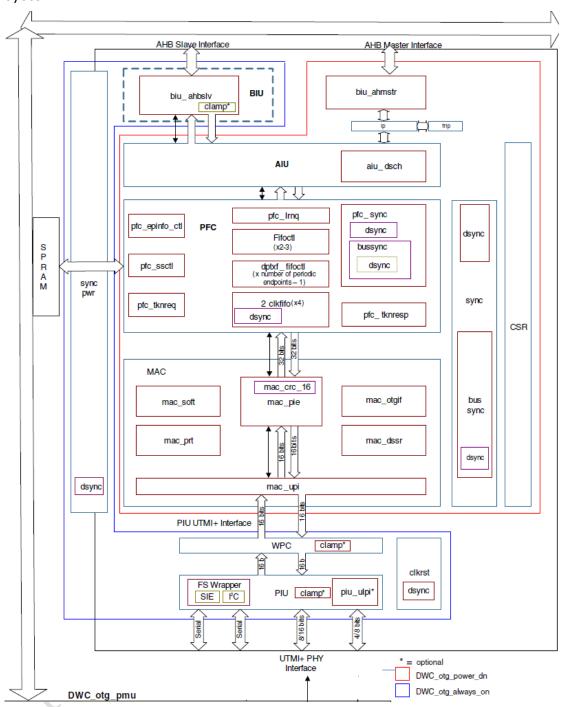

# 26.3 USB OTG2.0 Controller

Fig.26-4 shows the main components and flow of the USB OTG 2.0 controller

Rockchip RK3128 Technical Reference Manual Rev 1.0

Fig. 26-4 USB OTG2.0 Controller Architecture

1). AHB Slave Bus Interface Unit (BIUS)

The AHB Slave interface unit converts AHB cycles to CSR write/read, Data-FIFO read/write, and DFIFO push/pop signals.

2) Control and Status Registers (CSR)

The CSR block resides in the AHB clock domain, and contains all registers except the Power and Clock Gating Control Register (PCGCCTL) and bits 31:29 of the Core Interrupt register (GINTSTS).

3) Application Interface Unit (AIU)

The application Interface Unit (AIU) consists of the following interfaces:

- AHB Master

- AHB Slave

- Packet FIFO Controller

- Control and Status registers

- 4). DMA Scheduler (DSCH)

This block is used only in DMA mode. It controls the transfer of data packets between the system memory and the USB OTG 2.0 Controller for both Internal and External DMA.

5). Packet FIFO Controller (PFC)

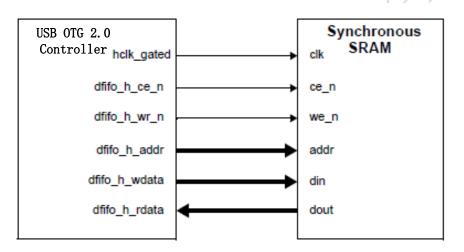

Several FIFOs are used in Device and Host modes to store data inside the core before transmitting it on either the AHB or the USB. PFC connect the Data FIFO interface to an industry-standard, single-port synchronous SRAM. Address, write data, and control outputs are driven late by the USB OTG 2.0 Controller, but in time to meet the SRAM setup requirements. Input read data is expected late from the SPRAM and registered inside the core before being used.

Fig. 26-5 DFIFO single-port synchronous SRAM interface

6).Media Access Controller (MAC)

The Media Access Controller (MAC) module handles USB transactions, and device, host, and OTG protocols.

7) PHY Interface Unit (PIU)

The core uses 16-bit UTMI+ Interface.

8) Wakeup and Power Controller (WPC)

When the USB is suspended or the session is not valid, the PHY is driven into Suspend mode and the PHY clock is stopped to reduce PHY and the core power consumption. To reduce power consumption further, the core also supports AHB clock gating and partial power-down.

### 26.3.1 Host Architecture

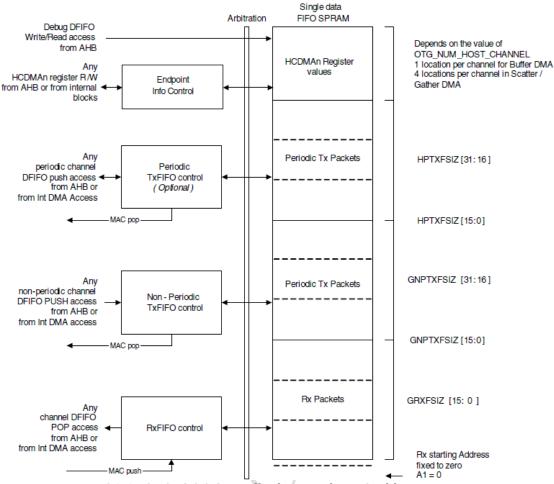

The host uses one transmit FIFO for all non-periodic OUT transactions and one transmit FIFO for all periodic OUT transactions. These transmit FIFOs are used as transmit buffers to hold the data (payload of the transmit packet) to be transmitted over USB.

The host pipes the USB transactions through Request queues (one for periodic and one for non-periodic). Each entry in the Request - queue holds the IN or OUT channel number along with other information to perform a transaction on the USB. The order in which the requests are written into the queue determines the sequence of transactions on the USB. The host processes the periodic Request queue first, followed by the non-periodic Request queue, at the beginning of each (micro) frame.

The host uses one Receive-FIFO for all periodic and non-periodic transactions. The FIFO is used as a Receive-buffer to hold the received data (payload of the received packet) from the USB until it is transferred to the system memory. The status of each packet received also goes into the FIFO. The status entry holds the IN channel number along with other information, such as received byte count and validity status, to perform a transaction on the AHB.

### **26.3.2 Device Architecture**

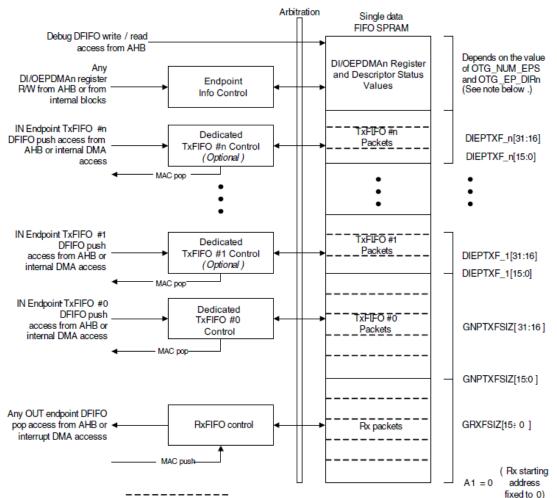

The core uses Dedicated Transmit FIFO Operation. In this mode, there are individual transmit FIFOs for each IN endpoint.

The OTG device uses a single receive FIFO to receive the data for all the OUT endpoints. The receive FIFO holds the status of the received data packet, such as byte count, data PID and the validity of the received data. The DMA or the application reads the data out of the receive FIFO as it is received.

### 26.3.3 FIFO Mapping

• Fig.26-6 shows FIFO mapping in Host mode.

Fig. 26-6 USB OTG 2.0 Controller host mode FIFO address mapping

*Note: When the device is operating in Internal DMA mode, the last locations of the SPRAM are used to store the DMAADDR values for each channel.*

• Fig.26-7 shows FIFO mapping in Device mode.

When the device is operating in non-Descriptor Internal DMA mode, the last locations of the SPRAM are used to store the DMAADDR values for each channel. When the device is operating in Descriptor mode, then the last locations of the SPRAM store the Base Descriptor address, Current Descriptor address, Current Buffer address, and status quad let information for each endpoint direction.

Fig. 26-7 USB OTG 2.0 Controller device mode FIFO address mapping

Note: When the device is operating in non-Scatter Gather Internal DMA mode, the last locations of the SPRAM are used to store the DMAADDR values for each Endpoint (1 location per endpoint). When the device is operating in Scatter Gather mode, then the last locations of the SPRAM store the Base Descriptor address, Current Descriptor address, Current Buffer address, and status quadlet information for each endpoint direction (4 locations per Endpoint). If an Endpoint is bidirectional, then 4 locations will be used for IN, and another 4 for OUT).

# 26.4 USB OTG2.0 PHY

USB PHY supports dual OTG ports' functions and is fully compliant with USB2.0 specification, and support High-speed (480Mbps), full-speed (12Mbps), low-speed (1.5Mbps) transfer. It provides a complete on-chip transceiver physical solution with ESD protection. A minimum number of external components are needed, which include a 45 ohm resistor for resistance calibration purpose. Its feature contains:

- provide dual UTMI ports

- OTG0 Support UART Bypass Function

• Fully compliant with USB specifications Rev 2.0, 1.1 HOST/Device and OTG V1.2.

- Supports 480Mbps (HS), 12Mbps (FS) & 1.5Mbps(LS) serial data transmission

- Supports low latency hub mode with 40 bit time round trip delay

- 8 bit or 16 bit UTMI interface compliant with UTMI+ specification level 3 Rev 1.

- Loop back BIST mode supported

- Built-in I/O and ESD structure

- On-die self-calibrated HS/FS/LS termination

- 12MHz crystal oscillator with integrated phase-locked loop (PLL) oscillator

- Manufactured in SMIC 65/55nm LL process

- Dual 3.3V / 1.2V supply

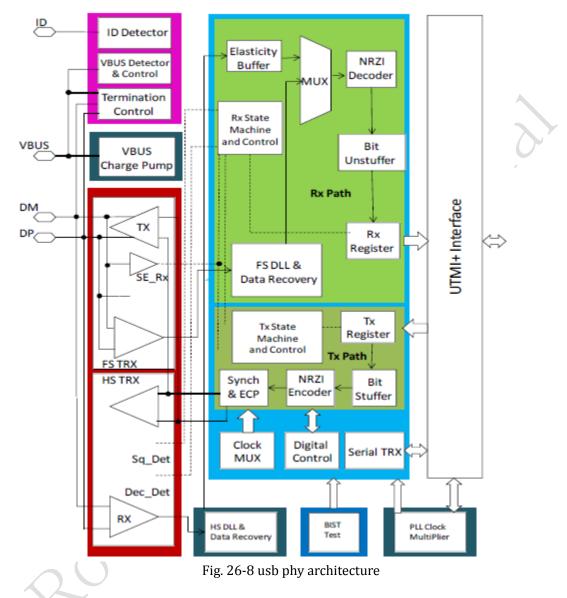

### 26.4.1 Block Diagram

#### **HS AFE**

The HS AFE contains the low-level analog circuitry, and also the HS differential data transmitter and receiver, to perform HS transmission envelope detection and host disconnection detection. It works in HS mode only.

#### **HS Transmit driver**

The HS transmit driver is active only when transmit is asserted. In HS transceiver enabled mode and the transmit state machine has data to send, the XCVR selects input. Data from transmit data path will be driven onto the DP/DM signal lines when enabled.

#### **HS Differential Receiver**

When enabled, received HS data will be multiplexed through the receive data path to the receive shift and hold registers. It is active only in HS mode.

transmission envelope detector (Squelch detector)

When the amplitude of the differential signal at a receiver's inputs falls below the squelch threshold, the envelope detector will indicate the invalid data. It must indicate squelch when the signal drops below 100mV differential amplitude, and also, it must indicate that the line is not in the squelch state when the signal exceeds 150mV differential amplitude.

#### **Disconnection envelope detector**

In host mode, this envelope detector is active to detect the high speed disconnect state on the line. Disconnection must be indicated when the amplitude of the differential signal at the downstream facing driver's connector is more than 625 mV, and it must not be indicated when the signal amplitude is less than 525 mV.

#### FS/LS AFE

In FS or LS mode, the FS/LS AFE is active to send and receive the FS or LS data on the USB bus. Also it supports the reset, suspend and resume detection through the data line single ended receivers.

#### **FS/LS** Transmitter

The FS/LHS transmitter is active only when transmit is asserted. In FS or LS transceiver enabled mode and the transmit state machine has data to send, the XCVR selects input. Data from transmit data path will be driven onto the DP/DM signal lines when enabled.

#### **FS/LS Differential Receiver**

When enabled, received FS or LS data will be multiplexed through the receive data path to the receive shift and hold registers. It is active only in FS or LS modes.

#### Single ended receivers

The single ended receivers are used for low-speed and full-speed signaling detection.

#### **Digital Core TX Path**

The digital core TX path has some blocks responsible for SYNC and EOP generation, data encoding, bit stuffing and data serialization. And meanwhile, also a TX state machine is involved to manage the communication with the controller.

#### TX Shift/Hold Register

The TX shift/Hold register module consists of an 8-bit primary shift register for parallel/serial conversion and 8-bit hold register used to buffer the next data to serialize. This module is responsible for reading parallel data from the parallel application bus interface upon command and serializing for transmission over USB.

#### **Bit stuffer**

To ensure adequate signal transitions, when sending a packet on USB, a bit stuffer is employed by the transmitter. A '0' has to be inserted after every six consecutive ones in the data stream before the data in NRZI encoded, to force a transition in the NRZI data stream.

#### NRZI Encoder

The High speed, Full speed or low speed serial transmitted data are encoded by The NRZI encoder. As a state transition, a '0' is encoded, and as no state transition, a '1' is encoded.

#### Transmit state machine

The communication between the controller and the PHY in TX path is controlled by the transmit state machine, which synchronizes the Data with the Sync and the EOP, and also supports the LS, FS and HS Modes.

#### Digital Core RX Path

The digital core RX path includes blocks responsible for SYNC and EOP detection and stripping, data decoding, bit un-stuffing and data de-serialization. Also a RX state machine is involved to manage the communication with the controller. FS/LS data and clock is recovered in this section.

#### **Elasticity buffer**

To compensate for differences between transmitting and receiving clocks, the Elasticity Buffer is used to synchronize the HS extracted data with the PLL internal clock.

#### Mux

The Mux block allows the data from the HS or FS/LS receivers to be routed to the shared receive logic. The state of the Mux is determined by the Xcvr Select input.

#### **NRZI Decoder**

The NRZI is responsible for decoding the High speed or Full speed received NRZI encoded data. A change in level is decoded as '0' and no change in level is decoded as '1'.

#### Bit Un-stuffer

The Bit Un-stuffer not only recognizes the stuffed bits from the data stream, but also discards them. Also it detects bit stuff error, which is interpreted as HS EOP.

#### **RX Shift/Hold Register**

This module de-serializes received data and transmits 8-bit parallel data to the application bus interface. It consists of an 8-bit primary shit register for serial to parallel conversion and an 8-bit hold register for buffering the last de-serialized data byte.

#### **Receiver state machine**

The receiver state machine controls the communication between the controller and the PHY in the RX path, strips the SYNC and the EOP from the Data and supports the LS, FS and HS Modes.

#### **PLL Clock Multiplier**

This module is composed of the off-chip crystal and the on-chip clock multiplier. It generates the appropriate internal clocks for the UTM and the CLK output signal. All data transfer signals are synchronized with the CLK signal.

#### **External Crystal**

The external crystal is composed of a precise resonance frequency crystal and a crystal oscillator. It is optional to have this crystal oscillator integrated on-chip

or have it off-chip. This crystal/crystal oscillator provides a very precise clock of 12 MHz with deviation of  $\pm 100$  ppm. The oscillator is not a part of the PHY, but external.

#### **Clock Multiplier**

The UTM interface is described as an un-directional/bi-directional 8-bit/16-bit parallel interface and the CLK signal is a 60/30 MHz signal. All data transfer signals should be synchronized with the CLK signal. CLK usable signal is internally implemented which blocks any transitions of CLK until it is usable. Meanwhile, the clock multiplier provides another three clocks in addition to the CLK signal. That is a480 MHz and 7.5 MHz clock signals.

#### **Clock MUX**

The Clock Multiplexer supplies both the transmitter and receiver paths with the adequate bit clock depending on the XcvrSelect signal and to ensure smooth clock switching. It also includes clock gating and power-down features.

#### **Control Logic Block**

This block is responsible for controlling, enabling and disabling the different blocks in the system.

#### **OTG Circuitry** (optional)

With the OTG circuitry, the system has the capability to dynamically switch between host and peripheral, enable dual role device behavior and point-to-point communication. The OTG circuitry functions as VBUS generation and detection. Both ID detection and terminations control are implemented in it.

#### **ID Detector** (optional)

To provide the ID signal that is used to indicate the state of the ID pin on the USB mini receptacle. This pin makes it able to determine which kind of plug is connected and to confirm if the device default state is A device or B device.

#### **VBUS Detector and termination control**

The VBUS detector is a set of comparators, functions to monitor and sense the voltage on USB bus power line. For VBUS signaling and discharging, VBUS pull up and pull-down resistors are also implemented.

#### **Automatic Test Functions**

• Loop-back test to address all IP components.

In loop-back test mode, all transmitted data packets are received back in an internal loop to check IP functional integrity. There are some digital components that cannot be tested with the scan technique due to the high-speed nature of the digital part. To be regarded as a good idea, Loop-back allows testing full design paths at speed. It should complement the testing suite for digital core to achieve the highest coverage possible. According to the UTMI specification Section 5.18, version 1.05 Page 34, the 8 bits un-directional data bus can be implemented as 8 bits bi-directional one. This implementation will hinder the loop-back test functionality.

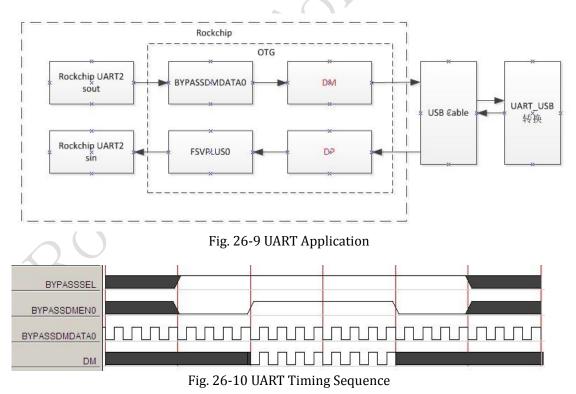

# **26.5 UART BYPASS FUNCITON**

When in UART bypass mode, UART2 is connect to USB interface; Otherwise, UART2 use normal UART interface.

| Rockchip<br><sub>瑞志徽电子</sub> RK3128 | Technical Reference Manual Rev 1.0 |

|-------------------------------------|------------------------------------|

|-------------------------------------|------------------------------------|

| Signal        | CONNECT      | I/O | Description                                                                                                                                                                                                                                                                                                                                    |

|---------------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYPASSDMDATA0 | uart2_sout   | I   | Data for DM0 Transmitter Digital<br>Bypass                                                                                                                                                                                                                                                                                                     |

| BYPASSDMEN0   | uoc0_con0[8] | Ι   | DM0 Transmitter Digital Bypass<br>Enable                                                                                                                                                                                                                                                                                                       |

| BYPASSSEL0    | uoc0_con0[9] | Ι   | Transmitter Digital Bypass mode<br>Enable                                                                                                                                                                                                                                                                                                      |

| FSVPLUS0      | uart2_sin    | 0   | Single-Ended D- Indicator<br>The controller signal indicates the<br>state of the DP during normal<br>operation or UART data reception                                                                                                                                                                                                          |

| OTGDISABLE0   | uoc0_con0[4] | Ι   | 1'b1: OTG0 disable;<br>1'b0: OTG0 normal mode                                                                                                                                                                                                                                                                                                  |

| COMMONONN     | uoc0_con0[0] | Ι   | Common Block Power-Down Control<br>This signal controls the power-down<br>signals in PLL blocks when the USB<br>PHY is in Suspend Mode.<br>1: PLL blocks are powered down.<br>0: PLL blocks remain powered<br>This signal is a strapping option that<br>must be set prior to a power-on<br>reset and remain static during<br>normal operation. |

#### Note: USB OTG2.0 PHY support UART Bypass Function.

To use UART and Auto resume functions:

1. Disable the OTG block by setting OTGDISABLE0 to 1'b1.

2. Disable the pull-up resistance on the D+ line by setting OPMODE0[1:0] to 2'b01.

3. To ensure that the XO, Bias, and PLL blocks are powered down in Suspend mode, set COMMONONN to 1'b1.

- 4. Place the USB PHY in Suspend mode by setting SUSPENDM0 to 1'b0.

- 5. Set BYPASSSEL0 to 1'b1.

- 6. To transmit data, controls BYPASSDMEN0, and BYPASSDMDATA0.

To receive data, monitor FSVPLUS0.

To return to normal operating mode:

- 1. Ensure that there is no activity on the USB.

- 2. Set BYPASSSEL0 to 1'b0.

- 3. Set SUSPENDM0 to 1'b1.Resume the USB PHY.

- 4. Set COMMONONN to 1'b0.

- 5. set OTGDISABLE0 to 1'b0.

### **26.6 Register Description**

#### 26.6.1 Register Summary

| 1                |        |      |                |                                                     |

|------------------|--------|------|----------------|-----------------------------------------------------|

| Name             | Offset | Size | Reset<br>Value | Description                                         |

| USBOTG_GOTGCTL   | 0x0000 | W    | 0x0000000      | Control and Status Register                         |

| USBOTG_GOTGINT   | 0x0004 | W    | 0x0000000      | Interrupt Register                                  |

| USBOTG_GAHBCFG   | 0x0008 | W    | 0x0000000      | AHB Configuration Register                          |

| USBOTG_GUSBCFG   | 0x000c | W    | 0x00001400     | USB Configuration Register                          |

| USBOTG_GRSTCTL   | 0x0010 | W    |                | Reset Register                                      |

| USBOTG_GINTSTS   | 0x0014 | W    | 0x0000000      | Interrupt Register                                  |

| USBOTG_GINTMSK   | 0x0018 | W    | 0x0000000      | Interrupt Mask Register                             |

| USBOTG_GRXSTSR   | 0x001c | w    | 0×00000000     | Receive Status Debug Read<br>Register               |

| USBOTG_GRXSTSP   | 0x0020 | w    | 0x00000000     | Receive Status Read and Pop<br>Register             |

| USBOTG_GRXFSIZ   | 0x0024 | W    | 0x0000000      | Receive FIFO Size Register                          |

| USBOTG_GNPTXFSIZ | 0x0028 | w    | 0x00000000     | Non-Periodic Transmit FIFO<br>Size Register         |

| USBOTG_GNPTXSTS  | 0x002c | W    | 0x0000000      | Non-Periodic Transmit<br>FIFO/Queue Status Register |

| USBOTG_GI2CCTL   | 0x0030 | W    | 0x11000000     | I2C Address Register                                |

| USBOTG_GPVNDCTL  | 0x0034 | W    | 0x0000000      | PHY Vendor Control Register                         |

| USBOTG_GGPIO     | 0x0038 | w    | 0x00000000     | General Purpose Input /<br>Output Register          |

| USBOTG_GUID      | 0x003c | W    | 0x0000000      | User ID Register                                    |

| USBOTG_GSNPSID   | 0x0040 | W    | 0x00004f54     | Core ID Register                                    |

| USBOTG_GHWCFG1   | 0x0044 | W    | 0x0000000      | User HW Config1 Register                            |

| USBOTG_GHWCFG2   | 0x0048 | W    | 0x0000000      | User HW Config2 Register                            |

| USBOTG_GHWCFG3   | 0x004c | W    | 0x0000000      | User HW Config3 Register                            |

| USBOTG_GHWCFG4   | 0x0050 | W    | 0x0000000      | User HW Config4 Register                            |

Sett

|                      |                        | <b>.</b> | Reset      | <b>_</b>                                                       |

|----------------------|------------------------|----------|------------|----------------------------------------------------------------|

| Name                 | Offset                 | Size     | Value      | Description                                                    |

| USBOTG_GLPMCFG       | 0x0054                 | W        | 0x00000000 | Core LPM Configuration<br>Register                             |

| USBOTG_GPWRDN        | 0x0058                 | W        | 0x0000000  | Global Power Down Register                                     |

| USBOTG_GDFIFOCF<br>G | 0x005c                 | w        | 0x00000000 | Global DFIFO Software<br>Configuration Register                |

| USBOTG_GADPCTL       | 0x0060                 | W        | 0x00000000 | ADP Timer, Control and<br>Status Register                      |

| USBOTG_HPTXFSIZ      | 0x0100                 | W        | 0x00000000 | Host Periodic Transmit FIFO                                    |

| USBOTG_DIEPTXFn      | 0x0104<br>+4*(n-<br>1) |          | 0x00000000 | Device Periodic Transmit<br>FIFO-n Size Register<br>n = 1 - 15 |

| USBOTG_HCFG          | 0x0400                 | W        | 0x0000000  | Host Configuration Register                                    |

| USBOTG_HFIR          | 0x0404                 | W        | 0x0000000  | Host Frame Interval Register                                   |

| USBOTG_HFNUM         | 0x0408                 | w        | 0x0000ffff | Host Frame Number/Frame<br>Time Remaining Register             |

| USBOTG_HPTXSTS       | 0x0410                 | W        | 0×00000000 | Host Periodic Transmit<br>FIFO/Queue Status Register           |

| USBOTG_HAINT         | 0x0414                 | W        | 0×00000000 | Host All Channels Interrupt<br>Register                        |

| USBOTG_HAINTMSK      | 0x0418                 | W        | 0×00000000 | Host All Channels Interrupt<br>Mask Register                   |

| USBOTG_HPRT          | 0x0440                 | W        | 0x0000000  | Host Port Control and Status<br>Register                       |

| USBOTG_HCCHARn       | 0x0500<br>+0x20<br>*n  | w        | 0x0000000  | Host Channel-n<br>Characteristics Register<br>n = 0 - 15       |

| USBOTG_HCSPLTn       | 0x0504<br>+0x20<br>*n  | w        | 0x00000000 | Host Channel-n Split Control<br>Register<br>n = 0 - 15         |

| USBOTG_HCINTn        | 0x0508<br>+0x20<br>*n  | W        | 0x00000000 | Host Channel-n Interrupt<br>Register<br>n = 0 - 15             |

| USBOTG_HCINTMSK<br>n | 0x050c<br>+0x20<br>*n  | w        | 0x00000000 | Host Channel-n Interrupt<br>Mask Register<br>n = 0 - 15        |

| USBOTG_HCTSIZn       | 0x0510<br>+0x20<br>*n  | W        | 0×00000000 | Host Channel-n Transfer Size<br>Register<br>n = 0 - 15         |

| USBOTG_HCDMAn        | 0x0514<br>+0x20<br>*n  | w        | 0×00000000 | n = 0 - 15                                                     |

| USBOTG_HCDMABn       | 0x051c<br>+0x20<br>*n  | w        | 0×00000000 | Host Channel-n DMA Buffer<br>Address Register<br>n = 0 - 15    |

| USBOTG_DCFG          | 0x0800                 |          |            | Device Configuration Register                                  |

| USBOTG_DCTL          | 0x0804                 |          |            | Device Control Register                                        |

| USBOTG_DSTS          | 0x0808                 | W        | 0x0000000  | Device Status Register                                         |

| USBOTG_DIEPMSK       | 0x0810                 | W        | 0x0000000  | Device IN Endpoint common<br>interrupt mask register           |

| Name                    | Offset                    | Size | Reset<br>Value | Description                                                       |

|-------------------------|---------------------------|------|----------------|-------------------------------------------------------------------|

|                         |                           |      | Value          | Device OUT Endpoint                                               |

| USBOTG_DOEPMSK          | 0x0814                    | W    | 0×00000000     | common interrupt mask<br>register                                 |

| USBOTG_DAINT            | 0x0818                    | W    | 0×00000000     | Device All Endpoints interrupt<br>register                        |

| USBOTG_DAINTMSK         | 0x081c                    | w    | 0×00000000     | Device All Endpoint interrupt<br>mask register                    |

| USBOTG_DTKNQR1          | 0x0820                    | w    | 0x00000000     | Device IN token sequence<br>learning queue read register1         |

| USBOTG_DTKNQR2          | 0x0824                    | w    | 0x00000000     | Device IN token sequence<br>learning queue read register2         |

| USBOTG_DVBUSDIS         | 0x0828                    | W    | 0x00000b8f     | Device VBUS discharge time<br>register                            |

| USBOTG_DVBUSPUL<br>SE   | 0x082c                    | W    | 0x0000000      | Device VBUS Pulsing Timer<br>Register                             |

| USBOTG_DTHRCTL          | 0x0830                    | W    | 0x08100020     | Device Threshold Control<br>Register                              |

| USBOTG_DIEPEMPM<br>SK   | 0x0834                    | W    | 0×00000000     | Device IN endpoint FIFO<br>empty interrupt mask<br>register       |

| USBOTG_DEACHINT         | 0x0838                    | W    | 0x00000000     | Device each endpoint<br>interrupt register                        |

| USBOTG_DEACHINT<br>MSK  | 0x083c                    | W    | 0×00000000     | Device each endpoint<br>interrupt register mask                   |

| USBOTG_DIEPEACH<br>MSKn | 0x0840<br>+4*n            | w    | 0x00000000     | Device each IN endpoint -n<br>interrupt Register<br>n = 0 - 15    |

| USBOTG_DOEPEACH<br>MSKn | 0x0880<br>+4*n            | w    | 0x00000000     | Device each out endpoint-n<br>interrupt register<br>n = 0 - 15    |

| USBOTG_DIEPCTL0         | 0x0900                    | W    | 0x00008000     | Device control IN endpoint 0 control register                     |

| USBOTG_DIEPINTn         | 0x0908<br>+0x20<br>*n     | w    | 0x00000000     | Device Endpoint-n Interrupt<br>Register<br>n = 0 - 15             |

| USBOTG_DIEPTSIZn        | 0x0910<br>+0x20<br>*n     | W    | 0x00000000     | Device endpoint n transfer<br>size register<br>n = 0 - 15         |

| USBOTG_DIEPDMAn         | 0x0914<br>+0x20<br>*n     | w    | 0x00000000     | Device endpoint-n DMA<br>address register<br>n = 0 - 15           |

| USBOTG_DTXFSTSn         | 0x0918<br>+0x20<br>*n     | w    |                | Device IN endpoint transmit<br>FIFO status register<br>n = 0 - 15 |

| USBOTG_DIEPDMAB<br>n    | 0x091c                    | w    | 0×00000000     | Device endpoint-n DMA buffer<br>address register                  |

| USBOTG_DIEPCTLn         | 0x0920<br>+0x20<br>*(n-1) | W    | 0x00000000     | Device endpoint-n control                                         |

| USBOTG_DOEPCTL0         | 0x0b00                    | W    | 0×00000000     | Device control OUT endpoint<br>0 control register                 |

| Name                 | Offset                    | Size | Reset<br>Value | Description                                                    |

|----------------------|---------------------------|------|----------------|----------------------------------------------------------------|

| USBOTG_DOEPINTn      | 0x0b08<br>+0x20<br>*n     | w    | 0×00000000     | Device endpoint-n control<br>register<br>n = 0 - 15            |

| USBOTG_DOEPTSIZn     | 0x0b10<br>+0x20<br>*n     | w    | 0x00000000     | Device endpoint n transfer<br>size register<br>n = 0 - 15      |

| USBOTG_DOEPDMAn      | 0x0b14<br>+0x20<br>*n     | w    | 0×00000000     | Device Endpoint-n DMA<br>Address Register<br>n = 0 - 15        |

| USBOTG_DOEPDMAB<br>n | 0x0b1c<br>+0x20<br>*n     | W    | 0×00000000     | Device endpoint-n DMA buffer<br>address register<br>n = 0 - 15 |

| USBOTG_DOEPCTLn      | 0x0b20<br>+0x20<br>*(n-1) | W    | 0×00000000     | Device endpoint-n control<br>register<br>n = 1 - 15            |

| USBOTG_PCGCR         | 0x0b24                    | W    | 0x200b8000     | Power and clock gating<br>control register                     |

Notes: <u>Size</u> : **B** - Byte (8 bits) access, **HW** - Half WORD (16 bits) access, **W** - WORD (32 bits) access

# 26.6.2 Detail Register Description

#### USBOTG\_GOTGCTL

Address: Operational Base + offset (0x0000) Control and Status Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                     |

|-------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:28 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                        |

| 27    | RW   | 0×0         | ChirpEn<br>Chirp on enable<br>This bit when programmed to 1'b1 results in<br>the core asserting chirp_on before sending an<br>actual Chirp "K" signal on USB. This bit is<br>present only if OTG_BC_SUPPORT = 1. If<br>OTG_BC_SUPPORT != 1, this bit is a reserved<br>bit.                                      |

| 26:22 | RO   | 0×00        | MultValidBc<br>Multi Valued ID pin<br>Battery Charger ACA inputs in the following<br>order:<br>Bit 26 - rid_float.<br>Bit 25 - rid_gnd<br>Bit 24 - rid_a<br>Bit 23 - rid_b<br>Bit 22 - rid_c<br>These bits are present only if<br>OTG_BC_SUPPORT = 1. Otherwise, these bits<br>are reserved and will read 5'h0. |

| 21    | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                        |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit   | Attr     | Reset Value | Description                                       |

|-------|----------|-------------|---------------------------------------------------|

|       |          |             | OTGVer                                            |

|       |          |             | OTG version                                       |

|       |          |             | Indicates the OTG revision.                       |

|       |          |             | 1'b0: OTG Version 1.3. In this version the core   |

| 20    | RW       | 0x0         | supports Data line pulsing and VBus pulsing       |

|       |          |             | for SRP.                                          |

|       |          |             | 1'b1: OTG Version 2.0. In this version the core   |

|       |          |             | supports only Data line pulsing for SRP.          |

|       |          |             | BSesVId                                           |

|       |          |             | B-session valid                                   |

|       |          |             | Indicates the Device mode transceiver status.     |

|       |          |             | 1'b0: B-session is not valid.                     |

|       |          |             | 1'b1: B-session is valid.                         |

|       |          |             | In OTG mode, you can use this bit to              |

| 19    | RO       | 0x0         | determine if the device is connected or           |

|       |          |             | disconnected. Note: If you do not enabled         |

|       |          |             | OTG features (such as SRP and HNP), the read      |

|       |          |             | reset value will be 1. The vbus assigns the       |

|       |          |             | values internally for non-SRP or non-HNP          |

|       |          |             | configurations.                                   |

|       |          |             | ASesVId                                           |

|       |          |             | A-session valid                                   |

|       |          |             | Indicates the Host mode transceiver status.       |

|       |          |             | 1'b0: A-session is not valid                      |

| 18    | RO       | 0x0         | 1'b1: A-session is valid                          |

| 10    | ĸŪ       | 0.00        | Note: If you do not enabled OTG features          |

|       |          |             | (such as SRP and HNP), the read reset value       |

|       |          |             | will be 1.The vbus assigns the values             |

|       |          |             | internally for non-SRP or non-HNP                 |

|       |          | • 4         | configurations.                                   |

|       |          |             | DbnTime                                           |

|       |          |             | Long/short debounce time                          |

|       |          |             | Indicates the debounce time of a detected         |

| 17    | RO       | 0x0         | connection.                                       |

|       |          |             | 1'b0: Long debounce time, used for physical       |

|       |          |             | connections (100 ms + 2.5 us)                     |

|       |          | )           | 1'b1: Short debounce time, used for soft          |

|       | $\frown$ |             | connections (2.5 us)                              |

|       |          |             | ConIDSts                                          |

|       |          |             | Connector ID Status                               |

| 16    | RO       | 0x0         | Indicates the connector ID status on a connect    |

|       |          |             | event.                                            |

|       |          |             | 1'b0: The core is in A-Device mode                |

| 15.12 |          | 0.20        | 1'b1: The core is in B-Device mode                |

| 15:12 | RO       | 0x0         | reserved                                          |

|       |          |             | DevHNPEn                                          |

|       |          |             | Device HNP Enable                                 |

|       |          |             | The application sets this bit when it             |

| 11    | RW       | 0x0         | successfully receives a SetFeature.               |

|       |          |             | SetHNPEnable command from the connected USB host. |

|       |          |             |                                                   |

|       |          |             | 1'b0: HNP is not enabled in the application       |

|       |          |             | 1'b1: HNP is enabled in the application           |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                          |

|-----|------|-------------|----------------------------------------------------------------------|

|     |      |             | HstSetHNPEn                                                          |

|     |      |             | Host set HNP enable                                                  |

|     |      |             | The application sets this bit when it has                            |

| 1.0 |      | 00          | successfully enabled HNP (using the                                  |

| 10  | RW   | 0x0         | SetFeature.SetHNPEnable command) on the                              |

|     |      |             | connected device.                                                    |

|     |      |             | 1'b0: Host Set HNP is not enabled                                    |

|     |      |             | 1'b1: Host Set HNP is enabled                                        |

|     |      |             | HNPReq                                                               |

|     |      |             | HNP request                                                          |

|     |      |             | The application sets this bit to initiate an HNP                     |

|     |      |             | request to the connected USB host. The                               |

|     |      |             | application can clear this bit by writing a 0                        |

| 9   | RW   | 0x0         | when the Host Negotiation Success Status                             |

| -   |      |             | Change bit in the OTG Interrupt register                             |

|     |      |             | (GOTGINT.HstNegSucStsChng) is set. The                               |

|     |      |             | core clears this bit when the                                        |

|     |      |             | HstNegSucStsChng bit is cleared.                                     |

|     |      |             | 1'b0: No HNP request<br>1'b1: HNP request                            |

|     |      |             | HstNegScs                                                            |

|     |      |             | Host Negotiation Success                                             |

|     |      |             | The core sets this bit when host negotiation is                      |

|     |      |             | successful. The core clears this bit when the                        |

| 8   | RO   | 0x0         | HNP Request (HNPReq) bit in this register is                         |

|     |      |             | set.                                                                 |

|     |      |             | 1'b0: Host negotiation failure                                       |

|     |      |             | 1'b1: Host negotiation success                                       |

| 7:2 | RO   | 0x0         | reserved                                                             |

|     |      | • •         | SesReq                                                               |

|     |      |             | Session Request                                                      |

|     |      |             | The application sets this bit to initiate a                          |

|     |      |             | session request on the USB. The application                          |

|     |      |             | can clear this bit by writing a 0 when the Host                      |

|     |      |             | Negotiation Success Status Change bit in the                         |

|     | C    |             | OTG Interrupt register                                               |

|     |      |             | (GOTGINT.HstNegSucStsChng) is set. The core clears this bit when the |

|     | ()   |             | HstNegSucStsChng bit is cleared. If you use                          |

| 1   | RW   | 0x0         | the USB 1.1 Full-Speed Serial Transceiver                            |

|     |      |             | interface to initiate the session request, the                       |

| Y   |      |             | application must wait until the VBUS                                 |

|     |      |             | discharges to 0.2 V, after the B-Session Valid                       |

|     |      |             | bit in this register (GOTGCTL.BSesVId) is                            |

|     |      |             | cleared. This discharge time varies between                          |

|     |      |             | different PHYs and can be obtained from the                          |

|     |      |             | PHY vendor.                                                          |

|     |      |             | 1'b0: No session request                                             |

|     |      |             | 1'b1: Session request                                                |

| Bit | Attr | Reset Value | Description                                                                                                                                                                          |

|-----|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | RO   | 0x0         | SesReqScs<br>Session Request Success<br>The core sets this bit when a session request<br>initiation is successful.<br>1'b0: Session request failure<br>1'b1: Session request success |

#### USBOTG\_GOTGINT

Address: Operational Base + offset (0x0004) Interrupt Register

| Bit   | Attr | <b>Reset Value</b> | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:21 | RO   | 0x0                | reserved                                                                                                                                                                                                                                                                                                                                                                      |

| 20    | W1C  | 0×0                | MultiValueChg<br>Multi-Valued input changed<br>This bit when set indicates that there is a<br>change in the value of at least one ACA pin<br>value. This bit is present only if<br>OTG_BC_SUPPORT = 1, otherwise it is<br>reserved.                                                                                                                                           |

| 19    | W1C  | 0×0                | DbnceDone<br>Debounce Done<br>The core sets this bit when the debounce is<br>completed after the device connection. The<br>application can start driving USB reset after<br>seeing this interrupt. This bit is only valid<br>when the HNP Capable or SRP Capable bit is<br>set in the Core USB Configuration register<br>(GUSBCFG.HNPCap or GUSBCFG.SRPCap,<br>respectively). |

| 18    | W1C  | 0×0                | ADevTOUTChg<br>A-Device Timeout Change<br>The core sets this bit to indicate that the<br>A-device has timed out while waiting for the<br>B-device to connect.                                                                                                                                                                                                                 |

| 17    | W1C  | 0×0                | HstNegDet<br>Host Negotiation Detected<br>The core sets this bit when it detects a host<br>negotiation request on the USB                                                                                                                                                                                                                                                     |

| 16:10 | RO   | 0x0                | reserved                                                                                                                                                                                                                                                                                                                                                                      |

| 9     | W1C  | 0×0                | HstNegSucStsChng<br>Host Negotiation Success Status Change<br>The core sets this bit on the success or failure<br>of a USB host negotiation request. The<br>application must read the Host Negotiation<br>Success bit of the OTG Control and Status<br>register (GOTGCTL.HstNegScs) to check for<br>success or failure                                                        |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                             |

|-----|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | W1C  | 0×0         | SesReqSucStsChng<br>Session Request Success Status Change<br>The core sets this bit on the success or failure<br>of a session request.The application must read<br>the Session Request Success bit in the OTG<br>Control and Status register<br>(GOTGCTL.SesReqScs) to check for success or<br>failure. |

| 7:3 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                |

| 2   | W1C  | 0×0         | SesEndDet<br>Session End Detected<br>The core sets this bit when the utmisrp_bvalid<br>signal is deasserted                                                                                                                                                                                             |

| 1:0 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                |

#### USBOTG\_GAHBCFG

| 1:0     | RU                                                                                          | UXU         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------|---------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Address | USBOTG_GAHBCFG<br>Address: Operational Base + offset (0x0008)<br>AHB Configuration Register |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Bit     | Attr                                                                                        | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 31:23   | RO                                                                                          | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 22      | RW                                                                                          | 0×0         | NotiAllDmaWrit<br>Notify All Dma Write Transactions<br>This bit is programmed to enable the System<br>DMA Done functionality for all the DMA write<br>Transactions corresponding to the<br>Channel/Endpoint. This bit is valid only when<br>GAHBCFG.RemMemSupp is set to 1.<br>GAHBCFG.NotiAllDmaWrit = 1.<br>HSOTG core asserts int_dma_req for all the<br>DMA write transactions on the AHB interface<br>along with int_dma_done, chep_last_transact<br>and chep_number signal informations. The<br>core waits for sys_dma_done signal for all the<br>DMA write transactions in order to complete<br>the transfer of a particular Channel/Endpoint.<br>GAHBCFG.NotiAllDmaWrit = 0.<br>HSOTG core asserts int_dma_req signal only<br>for the last transaction of DMA write transfer<br>corresponding to a particular<br>Channel/Endpoint. Similarly, the core waits<br>for sys_dma_done signal only for that<br>transaction of DMA write to complete the<br>transfer of a particular Channel/Endpoint. |  |  |  |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit  | Attr                                    | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------|-----------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |             | RemMemSupp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 21   | RW                                      | 0×0         | Remote Memory Support<br>This bit is programmed to enable the<br>functionality to wait for the system DMA Done<br>Signal for the DMA Write Transfers.<br>GAHBCFG.RemMemSupp=1.<br>The int_dma_req output signal is asserted<br>when HSOTG DMA starts write transfer to the<br>external memory. When the core is done with<br>the Transfers it asserts int_dma_done signal<br>to flag the completion of DMA writes from<br>HSOTG. The core then waits for<br>sys_dma_done signal from the system to<br>proceed further and complete the Data<br>Transfer corresponding to a particular<br>Channel/Endpoint.<br>GAHBCFG.RemMemSupp=0.<br>The int_dma_req and int_dma_done signals<br>are not asserted and the core proceeds with<br>the assertion of the XferComp interrupt as<br>soon as the DMA write transfer is done at the<br>HSOTG Core Boundary and it does not wait for<br>the sys_dma_done signal to complete the<br>DATA transfers. |  |  |  |

| 20:9 | RO                                      | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 8    | RW                                      | 0×0         | PTxFEmpLvl<br>Periodic TxFIFO Empty Level<br>Indicates when the Periodic TxFIFO Empty<br>Interrupt bit in the Core Interrupt register<br>(GINTSTS.PTxFEmp) is triggered. This bit is<br>used only in Slave mode.<br>1'b0: GINTSTS.PTxFEmp interrupt indicates<br>that the Periodic TxFIFO is half empty<br>1'b1: GINTSTS.PTxFEmp interrupt indicates<br>that the Periodic TxFIFO is completely empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 8    | Rock                                    |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit         | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7           | RW   | 0×0         | NPTxFEmpLvl<br>Non-Periodic TxFIFO Empty Level<br>This bit is used only in Slave mode. In host<br>mode and with Shared FIFO with device mode,<br>this bit indicates when the Non-Periodic<br>TxFIFO Empty Interrupt bit in the Core<br>Interrupt register GINTSTS.NPTxFEmp) is<br>triggered. With dedicated FIFO in device<br>mode, this bit indicates when IN endpoint<br>Transmit FIFO empty interrupt<br>(DIEPINTn.TxFEmp) is triggered.<br>Host mode and with Shared FIFO with device<br>mode:<br>1'b0: GINTSTS.NPTxFEmp interrupt indicates<br>that the Non-Periodic TxFIFO is half empty<br>1'b1: GINTSTS.NPTxFEmp interrupt indicates<br>that the Non-Periodic TxFIFO is completely<br>empty<br>Dedicated FIFO in device mode:<br>1'b0: DIEPINTn.TxFEmp interrupt indicates<br>that the IN Endpoint TxFIFO is half empty<br>1'b1: DIEPINTn.TxFEmp interrupt indicates |  |  |

|             |      |             | that the IN Endpoint TxFIFO is completely<br>empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 6           | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5           | RW   | 0x0         | DMAEn<br>DMA Enable<br>1'b0: Core operates in Slave mode<br>1'b1: Core operates in a DMA mode<br>This bit is always 0 when Slave-Only mode has<br>been selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Referenced. |      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:1 | RW   | 0x0         | HBstLen<br>Burst Length/Type<br>This field is used in both External and Internal<br>DMA modes. In External DMA mode, these<br>bits appear on dma_burst[3:0] ports, External<br>DMA Mode defines the DMA burst length in<br>terms of 32-bit words:<br>4'b0000: 1 word<br>4'b0001: 4 words<br>4'b0010: 8 words<br>4'b0101: 6 words<br>4'b0101: 64 words<br>4'b0101: 64 words<br>4'b0101: 64 words<br>4'b0111: 256 words<br>0thers: Reserved<br>Internal DMA Mode AHB Master burst type:<br>4'b0001: INCR<br>4'b0011: INCR4<br>4'b0011: INCR4<br>4'b0111: INCR16<br>Others: Reserved |

| 0   | RW   | 0×0         | GlblIntrMsk<br>Global Interrupt Mask<br>The application uses this bit to mask or<br>unmask the interrupt line assertion to itself.<br>Irrespective of this bit's setting, the interrupt<br>status registers are updated by the core.<br>1'b0: Mask the interrupt assertion to the<br>application.<br>1'b1: Unmask the interrupt assertion to the<br>application.                                                                                                                                                                                                                  |

### USBOTG\_GUSBCFG

Address: Operational Base + offset (0x000c) USB Configuration Register

| Bit | Attr | Reset Value | Description                                                                                              |

|-----|------|-------------|----------------------------------------------------------------------------------------------------------|

| 31  | RW   | 0×0         | CorruptTxpacket<br>Corrupt Tx packet<br>This bit is for debug purposes only. Never set<br>this bit to 1. |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                                |

|-----|------|-------------|--------------------------------------------------------------------------------------------|

|     |      |             | ForceDevMode                                                                               |

|     |      |             | Force Device Mode                                                                          |